# INTEGRATED COMPUTER ARCHITECTURE FOR PATTERN

ANALYSIS AND IMAGE DATABASE MANAGEMENT\*

ру

Kai Hwang and King-Sun Fu Purdue University May 1982

An integrated computer system for image processing, pattern recognition, and pictorial database management will further advance state-of-the-art development of machine intelligence systems for advanced automation.

<sup>\*</sup>This research is supported in part by NSF grant ECS-80-16580, and in part by the Institute of Information Science, Academia Sinica.

0022

Pattern analysis refers to the use of digital computers for Pattern Recognition and Image Processing (PRIP). On line imagery data needs to be stored on disks and fastly retrieved for PRIP applications. An effective pictorial information system requires both capabilities of efficiently managing and of fastly analyzing imagery data. This article presents a systematic approach to developing a special-purpose computer architecture for processing pictorial information. This approach integrates both patternanalysis and image-database-management capabilities into a unified design for the said purposes. The integrated design is aimed at the development of a real-time and interactive computer system for processing multi-dimensional information.

A state-of-the-art assessment is presented on various pattern-analysis machines constructed or being reported in the literature. We shall examine special database machines suggested for handling imagery data. Recent efforts on VLSI hardware approaches to implementing PRIP algorithms and to processing image queries will be discussed. The integrated architectural approach is initiated by the PUMPS architecture currently under development at Purdue University<sup>1,2</sup>. We shall identify the desired architectural features, processing languages, image databases, and underlying VLSI computing structures for developing such intelligent computer systems.

### PATTERN-ANALYSIS COMPUTERS

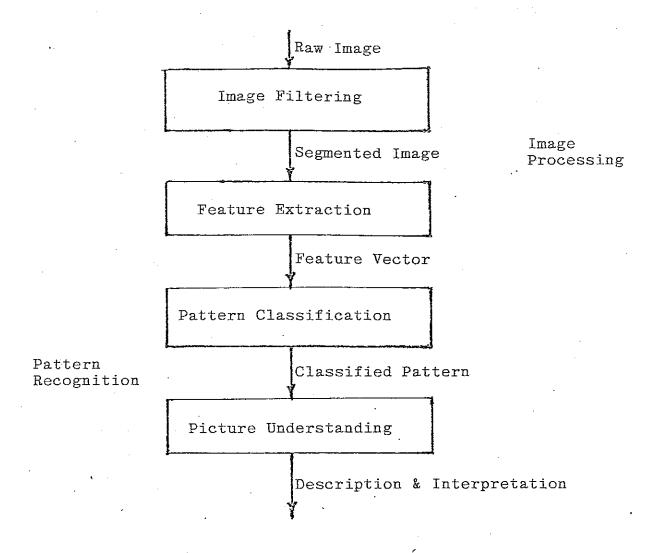

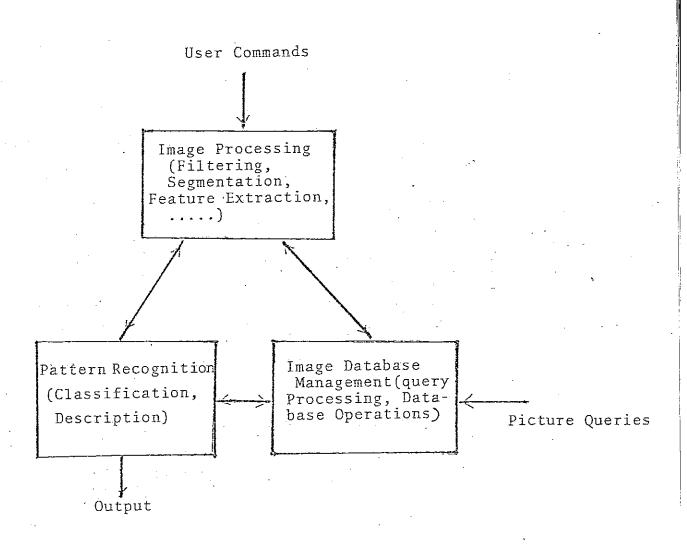

A typical pattern-analysis system consists of four processing stages as depicted in Fig.1. The <u>filtering</u> stage includes image operations like smoothing, enhancement, restoration, edge detection, and segmentation, etc. Raw images are reduced to segmented patterns by this initial stage. The second stage is for <u>feature extraction</u>, which further reduces the segmented image to a small set of feature vectors. Clustering techniques may be applied at this stage. The third stage is for <u>pattern classification</u>, which recognizes the membership of extracted features among known pattern classes. The fourth stage is for <u>pattern understanding</u>, which performs structural/texture analysis, shape discrimination, and 3-dimensional scene analysis to produce a brief description and precise interpretation of the pattern information<sup>3</sup>,45,48,49,51.

Conventional Single-Instruction and Single-Data Stream (SISD) computers are primarily designed to process one-dimensional strings of alphanumerical data. To process multi-dimensional information on SISD computers requires image coding and picture transformation (such as projection, registration, etc.)<sup>3</sup>. Sequential machines cannot efficiently exploit parallelism embedded in most PRIP operations. On the other hand, large parallel computers, such as Single-Instruction Multi-Data Stream (SIMD) array processors and

Fig.1 Processing stages of a pattern-analysis computer system

Multi-Instruction and Multi-Data stream (MIMD) multiprocessors, may not be necessarily cost-effective in implementing simple and repetitive image operations over very large and, sometimes, dynamically changing image databases.

An adequate pattern-analysis computer is expected to perform at least 100 megaflops with a memory bandwidth of at least 256 megabytes for applications in the 1980's, and many require to have processing power of 1000 megaflops or higher for those applications in the 1990's. Two excellent survey on special computer architectures for PRIP have been given by Fu<sup>4</sup> and by Danielsson and Levialdi<sup>5</sup>.

### ARCHITECTURAL REQUIREMENTS .

Identified below are desired architectural characteristics and functional features: of existing pattern-analysis computers. We focus on the interplay between computer architectures and PRIP applications. In general, a PRIP computer should be featured with as many of the following capabilities as possible:

(a) To explore spatial parallelism, a pattern-analysis computer may be equipped with replicated arithmetic/logic units operating synchronously in SIMD mode. Moreover, high degree of pipelining (temporal parallelism) is desired for overlapped instruction execution and pipelined vector arithmetic<sup>6</sup>,47.

- (b) Some PRIP computers choose a multiprocessor configuration to support asynchronous computations in MIMD mode. Data flow multiprocessor systems have been also suggested for PRIP or Artificial Intelligence computations 7.

- (c) Hierarchical memory system is needed for image storage and manipulation. Large main memory with fast image cache must be employed to alleviate the problem of image data overflow. Fast and intelligent I/O and sensing devices are needed for interactive pattern analysis and image query processing<sup>8</sup>.

- (d) Special image database management systems or image database machines are demanded for fast image information retrieval. Toward this end, some high-level picture description/manipulation languages need to be developed, in addition to developing image query languages 9,10,11.

- (e) PRIP computers should fully utilize state-of-the-art hard-ware component, and available software packages. Dedicated VLSI devices are needed for PRIP at signal-processing level and at symbol-manipulation level. Special VLSI pattern recognizers and image filtering chips are needed for fast image/picture construction, thresholding, FFT, histogram analysis, feature selection, and syntax analysis 12,13,14.

### EXISTING SYSTEM ARCHITECTURES

The architectures of PRIP machines can be divided into three categories: SIMD <u>array processors</u>, <u>pipelined vector processors</u>, and MIMD <u>multiprocessor systems</u>. Summarized in Table 1 are various pattern-analysis computers, their architectural configurations, and reported applications.

The use of an SIMD array of Processing Elements (PEs) for solving spatial image problems has been realized in Illiac IV15,  ${\tt STARAN}^{16}$ , CLIP Series<sup>17</sup>, and  ${\tt MPP}^{18}$ . In Illiac IV, image arrays structured other than 8 x 8 standard size must be partitioned into segmented loops in order to be properly processed by the 64 PE's. So far, Illiac IV has been applied for processing LANDSAT image, synthetic aperture radar signals, texture analysis, and linear programming image enhancement 19. The STARAN is an associative processor with 256 PEs updating a multi-dimensional-access memory. STARAN has been applied in NASA's Large Area Crop Inventory Experiments (LACIE) 20, and in implementing a digital cartographic system for the Defense Mapping Agency 21. CLIP IV is a cellular logic machine  $^{22}$  with 96 x 96 bit-slice PE's. It is specially designed for parallel window and neighborhood operations. is a bit-slice array processor with 128 x 128 PE's operating in lockstep. It is to be used mainly in processing satellite pictures for NASA<sup>23</sup>.

Summary of Pattern-Analysis Computers and Applications Table 1.

3

us

o

| ī | 1                           | 1                                                                |                                                                                                               |                                                                                                     |                                                                                                     |                                                                  |                                                                 |

|---|-----------------------------|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------|

|   | Reported Applications       | Landsat Images, Sythetic<br>Aperture Radar Signal<br>Processing. | NASA's LACIE Experiments,<br>Image Magnification, Con-<br>volution, Cartography for<br>Defense Mapping Agency | Window and Neighborhood<br>Operations for Bit-Plan<br>Image Processing and Fea-<br>ture Extraction. | Landsat Image Processing,<br>Target Screening, Tactical<br>Reconnaissance.                          | Cytology Analysis, Blomedi-cal Image Processing                  | General Image Processing<br>and Pattern Classification          |

|   | Status/<br>References       | Operational<br>Since 1972.<br>[15], [19]                         | Operational<br>Science 1974<br>[16],[20],<br>[21]                                                             | Operational V<br>since 1976<br>[5],[9],[17],<br>[22],[42],[51]                                      | rr To be deli- La<br>vered to NASA Ta<br>in 1982, [5], Re<br>[18],[23],<br>[51]                     | Under deve-<br>lopment as<br>of 1982 [5],<br>[8],[24],[27]       | Under deve-<br>lopment as<br>of 1982 [9],<br>[25]               |

|   | Developer/<br>Constructor   | Univ. of<br>Illinois/<br>Burroughs Co.                           | Goodyear<br>Aerospace Co.                                                                                     | University<br>College of<br>London                                                                  | NASA/Goodyear<br>Aerospace Co.                                                                      | Environmental<br>Research Ins-<br>titute of<br>Michigan          | Linkoeping<br>Univ., Sweden                                     |

|   | Machine Architecture        | SIMD, 64 PE's connected by an Mesh 8 x 8 mesh network            | SIMD, 32 arrays, 256 PE's per array, Associative, bit-slice structure, Flip Net-work.                         | SIMD, bit-slice<br>Cellular Mesh, 96 x 96<br>PE's. 8 Neighbors per<br>PE, NMOS/LSI Circuits.        | SIMD, 128 x 128 PE's,<br>Bit-Slice PE, RAM<br>memory planes. Mesh<br>Network, Custom VLSI<br>Chips. | Pipelined with 88 processor stages of one type and 25 of another | 4 Arithmetic Pipes, with staged memory and Microprogram Control |

|   | Pattern Analysis<br>Machine | ILLIAC-IV                                                        | STARAN                                                                                                        | CLIP-4                                                                                              | МРР                                                                                                 | Cytocomputer                                                     | GOP                                                             |

Summary of Pattern-Analysis Computers and Applications (continued) Table 1.

| Pattern Analysis<br>Machine | <u> </u>                                 | Machine Architecture                                                                        | Developer/<br>Constructor                                      | Status/<br>References                                  | Reported Applications                                                                |

|-----------------------------|------------------------------------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------------------------------------|

| Systolic<br>Processor       | Systolic<br>driven b<br>11/780 h         | c pipeline<br>by a VAX-<br>host                                                             | ESL/TRW, Advanced Processor Tech. Lab., San Jose               | Under Construction<br>1982, [26]                       | Signal/Image Processing,<br>2-D Convolution and<br>Resampling, FFT Opera-<br>tions   |

| PICAP-II                    | Modular<br>bus-str<br>Multipr<br>MIMD/SI | open-ended<br>uctured<br>ocessor<br>MD                                                      | Linkoping<br>University,<br>Sweden                             | Basic System operational 1980, [5], [30]               | Image Processing,<br>Computer Graphics.                                              |

| FLIP                        | 16 P)<br>Recognath<br>Matcro             | 16 Processors, MIMD,<br>Recogligurable Data-<br>path Pipelines,<br>Microprogrammable        | Research<br>Inst. for<br>IPPR, Karl-<br>sruhe, West<br>Germany | Under deve-<br>lopment as<br>of 1982,<br>[9], [33]     | General image processing and pattern recognition                                     |

| TOSPICS                     | Bus-st<br>procest<br>declic<br>functi    | ructure multi-<br>ssor system with<br>cated PRIP<br>lons and fast<br>memory                 | Toshiba Co.,'Japan                                             | Operational<br>since 1978,<br>[5],[31],<br>[50]        | Logical filtering, Region<br>Labeling, Two-dimensional<br>Convolution, Histogramming |

| ZMOB                        | 256<br>inte<br>pipe<br>Mode              | lcro-processors<br>connected by<br>ined bus, MIMD                                           | University of<br>Maryland                                      | Under Con-<br>struction<br>1982 [5],[32],<br>[34],[51] | Artificial Intelligence,<br>Image Processing.                                        |

| PUMPS                       | Multip<br>with s<br>device<br>image      | Multiprocessor system with shared functional device pool and backend image database machine | Purdue Uni-<br>versity                                         | Under deve-<br>lopment as<br>of 1982,[1],<br>[2],[52]  | Pattern Analysis, Image<br>Processing, Image Database<br>Wanagement.                 |

|                             |                                          |                                                                                             |                                                                |                                                        | _                                                                                    |

GC hi

pi

bi

fc

mι

ir

r

p:

Κı

0]

a.

F

Т

o

S

p

i.

p

C

Pipelined machines for PRIP include the cytocomputer<sup>24</sup>, the GOP<sup>25</sup>, and the ESL/systolic processor<sup>26</sup>. The cytocomputer is highly pipelined with a bandwidth of 1.6M bytes per second over 113 pipeline stages. It was mainly designed for cytology analysis and biomedical image processing<sup>27</sup>. The GOP image processor, containing four computation pipelines, can work on grey-scale, color, or multisepctral images of various sizes. It has been applied in image filtering, edge/line detection, texture description, relaxation, and classification operations. The ESL/systolic processor is based on the systolic pipeline structure proposed by Kung and Leiserson<sup>28</sup>. It is developed for signal/image processing operations like multi-dimensional convolution and resampling<sup>29</sup>.

Several MIMD multiprocessor systems were developed for PRIP applications. Among them are the PICAP-II<sup>30</sup>, TOSPICS<sup>31</sup>, ZMOB<sup>32</sup>, FLIP<sup>33</sup>, and PUMPS<sup>1,52</sup>.PICAP-II is a bus-structured multiprocessor. The bus allows 15 processors to be connected under the coordination of a host computer SEL 77/35. Some of the processors are themseleves SIMD array processors. The PICAP has been applied mainly in image processing research. TOSPICS is developed at Toshiba Corporation in Japan. It is also bus-structured with a number of dedicated processors for logical filtering, region labeling and two-dimensional convolution. A comprenhensive treatment of pattern recognition machines in Japan is given in the paper by Kidode<sup>50</sup>.

ZMOB is under development at University of Maryland. It consists of 256 Zilog 80A 8-bit microprocessors. It is designed for artificial intelligence and general computer science research. So far, it has been planned for image operations like discrete transforms, geometric operations, and computation of image statistics<sup>34</sup>. The FLIP is an image multiprocessor suitable for window operations by 16 individual processors in either MIMD or SIMD mode under the control of a host machine. It can process a 512 x 512 image in about one second. PUMPS is an MIMD machine with an integrated architecture for pattern analysis and image database management.

## IMAGE DATABASE MANAGEMENT

An image database system provides a large collection of structured imagery data (digitized pictures) for easy access by a large number of users. Existing image database systems and their reported applications are summarized in Table 2. Most of these image database systems are implemented with specially developed software packages upon dedicated pattern analysis systems.

Interested readers may refer to references 10,11,35,36,37 for some details of these systems. It is highly desirable to develop a dedicated backend database machine for image database management. Several hardware attempts were suggested 1,38,39. But none of them has been implemented yet.

Table 2. Summary of Image Database Systems and Reported Applications

| Image<br>Darabase<br>System | Developer, Year of<br>Introduction, and<br>Reference                                       | Implementation Approach and Capabilities                                                                                     | Reported Key<br>Applications                                                                                                  |

|-----------------------------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| IBIS                        | Bryant/Zobrist,<br>Jet Propulsion<br>Laboratory,<br>1977, [36]                             | Built upon existing VICAR image analysis system, Vedio Image Communication and retrieval                                     | Pictorial in-<br>formation<br>processing of<br>LANDSAT data<br>for geographic<br>analysis                                     |

| IMAID                       | Chang/Fu, Purdue<br>University, 1978,<br>[10]                                              | Relational model, using Query-by- Pictorial Examples, interfaced with an image analysis system and spatial operators         | Picture Manipu-<br>lation, and simi-<br>larity retrieval<br>for research on<br>advanced pattern<br>analysis and<br>automation |

| CGIS                        | Tomlinson, Cana-<br>dian Environmental<br>Department, 1968,<br>[53]                        | Use command and assessment languages, Overlapping of maps, interactive graphics, polygon representation                      | and regional                                                                                                                  |

| GADS                        | Mantey/Carlson,<br>IBM, San Jose,<br>1979, [54]                                            | Relational model,<br>built-in relational<br>operators, inter-<br>active data access.                                         | Geodata analysis<br>and display<br>system                                                                                     |

| MIDAS                       | McKeown/Reddy,<br>1977,[55]                                                                | Hierarchical model,<br>a multisensor image<br>database system                                                                | Image understand-<br>ing and knowledge<br>acquisition                                                                         |

| GEQ-QUEL                    | Berman/Stone-<br>bracker, Univer-<br>sity of California<br>at Berkeley, 1977,<br>[56]      | Relational model, in-<br>tegrated with INGRES<br>database system using<br>QUEL query language                                | phic data                                                                                                                     |

| GRAIN                       | Chang/Reduss/<br>McCormick, Univer-<br>sity of Illinois<br>at Chicago Circle<br>1977, [57] | Relational database with hierarchical structure, Various image retrieval functions Logical zooming, algebraic interpretation | Pictorial infor-<br>mation retrieval<br>and manipulation,<br>knowledge system<br>research                                     |

| SID                         | Kunii/Harada Uni-<br>versity of Tokyo,<br>1980, [58]                                       | Relational model,<br>Interactive design<br>using recensively<br>structured graphs.                                           | Computer-Aided Design (CAD) of software and elec- tronic circuits and engineering drawing evolution                           |

| IMDS                        | Lien/Utter, Uni-<br>versity of Kensas,<br>1977, [59]                                       | Relational model,<br>Using 1Q command<br>language store both<br>image and image<br>registrations                             | Image retrieval<br>and query language<br>research                                                                             |

| POLYVRT                     | Chrisman/Little,<br>Harvard University<br>1978, [60]                                       | A polygon approach<br>through line segment<br>chaining. Overlay<br>and Merge functions                                       | Research on<br>Computer graphics<br>and spatial analy-<br>sis                                                                 |

### VLSI PRIP ALGORITHMS

Recent advances in VLSI micro-electronic technology has triggered the thought of implementing some PRIP algorithms directly in hardware. VLSI pattern recognizers offer high speed and accuracy which are useful in real-time, on-line, pictorial information processing. This is the first step towards advanced automation and machine intelligence. Recently, many attempts have been made in developing special VLSI devices for signal/image processing and pattern recognition 12,13,14,26,29,40,41,42. Most of these approaches involve large-scale matrix computations or syntatic parsing operations. We list in Table 3 some candidate PRIP algorithms that might be suitable for VLSI implementation.

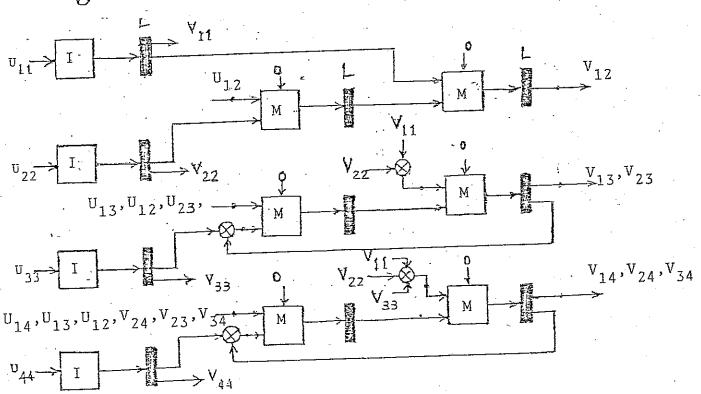

Two concrete design examples are presented below to illustrate the VLSI approaches to high-speed pattern recognition and image analysis. The first example presents some matrix manipulation networks for statistical feature extraction. The second example shows a two-dimensional pipeline for fast recognition of context-free languages. "Partitioned" matrix algorithms 43 can be applied for VLSI L-U decomposition, matrix multiplication, matrix inversion, and solving triangular systems of equations. Pipelined VLSI networks have been developed to realize these partitioned matrix algorithms 12. Figure 2 shows the functional design of a pipelined VLSI matrix inverter.

Table 3. Pictorial Information Processing Algorithms for Possible VLSI Implementation

| Image Processing             | Enhancement, Filtering, Fhining, Edge<br>Detection, Segmentation, Registration,<br>Restoration, Clustering, Texture<br>Analysis, Convolution, Fourier Analysis,<br>etc.                                                            |  |  |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pattern Recognition          | Statistical Classification, Graph Algorithms, Syntax Analysis, Change Detection, Language Recognition, Scene Analysis and Synthesis, etc.                                                                                          |  |  |

| Image Query Pro-<br>cessing  | Query Decomposition, Query Optimization, Attribute Manipulation, Picture Reconstruction, Search/Sorting Algorithms, Query-by-Picture-Example Implementation, etc.                                                                  |  |  |

| Image Database<br>Processing | Relational Operators (JOIN, UNION, INTER-<br>SECTION, PROJECTION, COMPLEMENT), Image-<br>Shetch-Relation Conversion, Similarity<br>Retrieval, Data Structures, Priority<br>Queues, Dynamic Programming, Spatial<br>Operators, etc. |  |  |

$$\mathbf{u}^{-1} = \begin{pmatrix} \mathbf{u}_{11} & \mathbf{u}_{12} & \mathbf{u}_{13} & \mathbf{u}_{14} \\ \mathbf{0} & \mathbf{u}_{22} & \mathbf{u}_{23} & \mathbf{u}_{23} \\ \mathbf{0} & \mathbf{0} & \mathbf{u}_{33} & \mathbf{u}_{34} \\ \mathbf{0} & \mathbf{0} & \mathbf{0} & \mathbf{u}_{44} \end{pmatrix}^{-1} = \begin{pmatrix} \mathbf{v}_{11} & \mathbf{v}_{12} & \mathbf{v}_{13} & \mathbf{v}_{14} \\ \mathbf{0} & \mathbf{v}_{22} & \mathbf{v}_{23} & \mathbf{v}_{24} \\ \mathbf{0} & \mathbf{0} & \mathbf{v}_{33} & \mathbf{v}_{34} \\ \mathbf{0} & \mathbf{0} & \mathbf{0} & \mathbf{v}_{44} \end{pmatrix} = \mathbf{v}$$

All  $U_{ij}$  and  $V_{ij}$  are  $m \times m$  submatrices . U and V are both  $n \times n$  The case of k = n/m = 4 is shown.

L: Latch

I : Submatrix Inverter

⊗ : Multiplexer

M : Submatrix Multiplier

$\mathbf{m}$

Fig. 2 VLSI Architecture for pipelined matrix inversion

Each square block shown in Fig. 2 corresponds to a VLSI matrix arithmetic device for handling submatrix computations. The input is an n x n upper triangular matrix U partitioned into  $k^2$  submatrices of dimension m x m such that  $n=k\cdot m$ . The case of k=n/m=4 is shown in Fig.2. Listed below are required submatrix computations in four sequential steps to generate the inverse matrix V in a partitioned fashion. Note that  $U_{ij}$  and  $V_{ij}$  are m x m submatrices and  $U_{ii}$  and  $V_{ii}$  are upper-triangular submatrices. Partitioned Matrix Inversion (for the case of k=n/m=4).

Step 1.  $V_{ii} = U_{ii}^{-1}$  for i = 1,2,3,4

34

Step 2.  $V_{i,i+1} = -V_{ii} \cdot (U_{i,i+1} \cdot V_{i+1,i+1})$  for i = 1,2,3

Step 3.  $V_{i,i+2} = -V_{ii} \cdot (U_{i,i+1} \cdot V_{i+1,i+3} + U_{i,i+2} \cdot V_{i+2,i+2})$ ; for i = 1,2

Step 4.  $V_{14} = -V_{11} \cdot (U_{12} \cdot V_{24} + U_{13} \cdot V_{34} + U_{14} \cdot V_{44})$

The I-modules are used to perform the inversion of the m x m upper-triangular submatrices at Step 1. The M-modules are used to perform the cumulative matrix multiplications specified in Step 2 through Step 4. The inputs and outputs at four successive computation steps are indicated at the I/O terminals in Fig.2. In general, inverting an n x n triangular matrix using this VLSI pipeline requires to use k I-modules and 2(k-1) M-modules. Thus the total VLSI module count equals O(k) = O(n/m) for n >> m. The

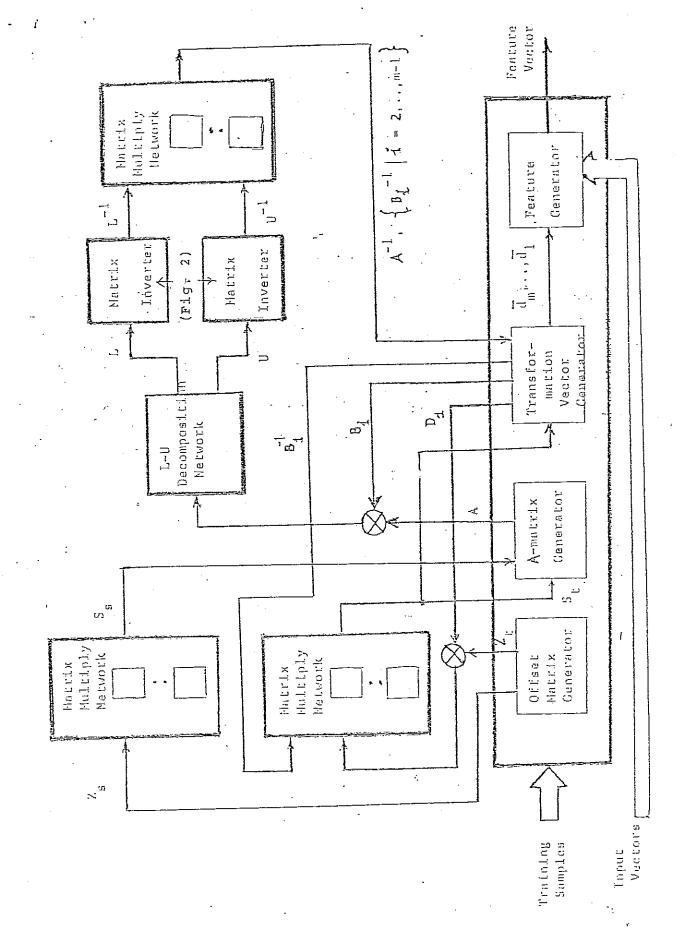

total time delay to generate  $V = U^{-1}$  equals  $O(n^2/m)$  for n >> m. An application of these VLSI matrix manipulation networks is shown in Fig.3 for the construction of a hardware feature extractor based on Foley and Sammon's algorithm<sup>44</sup>. The network subsystems for matrix multiply, L-U decomposition, and training sample manipulation can be similarly constructed with aforementioned VLSI arithmetic modules. Details of these VLSI matrix solvers can be found in 12,43.

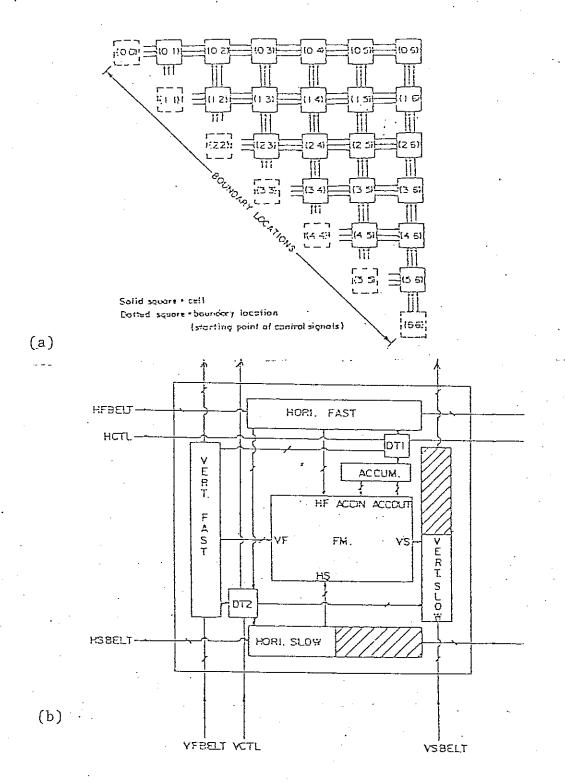

A VLSI pipelined array for high-speed recognition of context-free languages is shown in Fig.4.a. This pipelined array can be applied in syntactic pattern recognition 45. The array is constructed with n(n + 1)/2 processing cells, each of which assumes the functional structure shown in Fig.4.b. This two-dimensional array can recognize any input string of length n in 2n time units. The recognition process is based on the Cocke-Kasami-Younger algorithm. Details of this context-free language recognizer and its extension to recognize finite-state languages can be found in Ref.14. Similar VLSI approaches can be extended to other PRIP algorithms as listed in Table 3, including some for image query language processing and image database operations.

## THE INTEGRATED ARCHITECTURE

The three functions, image processing pattern recognition, and image database management, must be integrated into an efficient pictorial information system. A data-flow block diagram of such an integrated system is shown in Fig. 5. Three subsystems

∍d

no.

:3

ted onal.

.on

ıg-

t

Fig. 3 VLST Matrix manipulation network for statistical feature extraction

17

Fig. 4 VLSI architecture for fast recognition of context-free

languages

Fig. 5 Data flow diagram of an integrated computer system for pattern analysis/image database management

correspond to the three addressed functions. These subsystems must interact and cooperate with each other to achieve the said objectives. The user communicates with the system through some pictorial query language. The raw images are physically stored on disks (or tapes). A relational image database is established by mapping the physical images into the logically structured database. The image processing subsystem performs image filtering and feature extraction. The pattern recognition subsystem performs pattern classification and picture understanding operations. The image management subsystem handles query processing and image database operations.

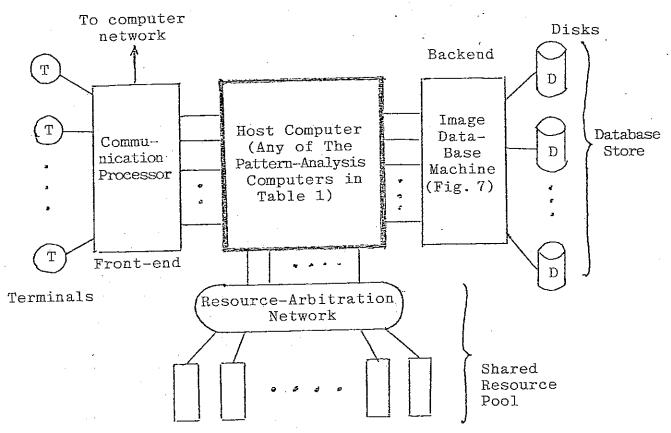

The system architecture of such an integrated picture processing computer is conceptually illustrated in Fig.6. The system consists of four major subsystems, as shown by the major blocks in the drawing. The host computer can be any one of those pattern-analysis computers listed in Table 1. The backend database machine is specially developed for image database management. Either software or hardware approaches can be adopted in developing image database management systems as summarized in Table 2. The front-end communication processor is used to handle terminal activities or to be connected to a computer network for remote users. The shared resource pool contains VLSI functional units or attached special processors for fast PRIP operations as examplified in Table 3. A resource arbitration network is needed between the host processors and the shared resource pool.

VLSI Devices for Image Processing and Recognition

Fig.6 Architecture of the integrated computer system for pattern analysis and image database management

One of the attempts to realize such an integrated computer system is the PUudue MultiProcessor System (PUMPS) architecture The bost computer in PUMPS is a multiprocessor system which can operate in either MIMD mode or in Multiple-SIMD mode or Multiple-SISD mode. The detailed system architecture of PUMPS has been presented in Ref.1. The system host consists of n uniprocessors sharing m memory modules through an Inter-Processor-Memory The resource pool of special-purpose VLSI functional units and peripheral processors is shared by all n processors. database machine can directly transfer information from the database store (disks) to the shared memory modules in PUMPS. Special VLSI devices in the resource pool can be dynamically allocated to multiple processors in the host system for carrying out its assigned functions. They can be also cascaded together as a dynamic pipeline for chained vector operations. Shared cache memories can be also used between the local processor memories and the shared memories in order to facilitate MIMD operations.

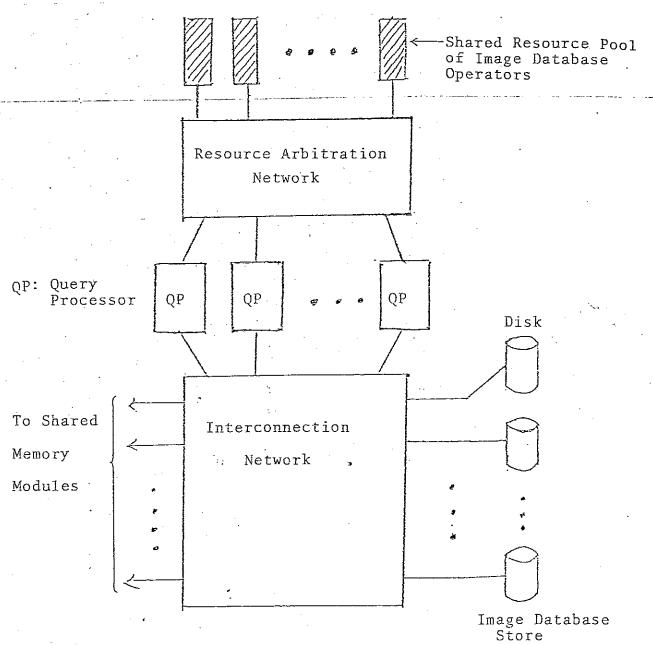

Presented in Fig.7 is a back-end image database machine. It is itself a multiprocessor system for parallel query processing and image database management. This structure is very similar to the DIRECT architecture 46, with multiple query processors accessing a set of shared data banks. We add a set of VLSI database functions that can be shared by the parallel query processors. Again, a resource sharing network is needed between the query processors and shared VLSI database operators. The shared database operators could be used for data filtering, projection, join or other operations if relational image database is established. Some VLSI database operators were listed in Table 3.

Fig.7 A multiprocessor image database machine with shared resource pool of VLSI Database Manipulators

### CONCLUSIONS

After examining existing pattern-analysis computers and image database systems, the system designer can easily realize the fact that the two addressed functions cannot be separated in an efficient pictorial information system. The integrated system approach is well supported by the merging VLSI technology and VLSI computing structures. Cost-effectiveness is the key issue in developing special-purpose machines for image processing, recognition, and database management. Such integrated computer architecture will further advance state-of-the-art development of machine intelligence systems for advanced automation, knowledge processing, and artificial intelligence.

#### REFERENCES:

- [1] Briggs, F. A., Hwang, K., Fu, K. S., and B. W. Wah, "PUMPS Architecture for Pattern Analysis and Image Database Management," Proc. Workshop Comp. Arch. for PAIDM, Hot Springs, Virginia, 1981, pp.178-187.

- [2] Fu, K. S. and Chang, N. S., "An Integrated Image Analysis and Image Database Management System," Proc. COMPCON, Fall, 1982.

- [3] Rosenfeld, A. and Kak, A. C. <u>Digital Picture Processing</u>, Academic Press, New York, 1976.

- [4] Fu, K. S., "Special Computer Architectures for Pattern Recognition and Image Processing," Proc. of National Computer Conf., Vol., AFIPS Press, 1978, pp.1003-1013.

- [5] Danielsson, P. E. and Levialdi, S., "Computer Architectures for Pictorial Information Systems," Computer, IEEE Computer Society, November 1981, pp.53-67.

- [6] Hwang, K., Su, S. P. and Ni, L. M. "Vector Computer Architecture and Processing Techniques," in Advances in Computers, Vol.20 (Yovits, Ed.) Academic Press, 1981. pp.115-197.

- [7] Amamiya, M., Hasegawa, R., and Mikami, H., "List Processing on A Dataflow Machine", in Research Reports in Japan, The Fifth Generation Computer Project, JIPDEC, Tokyo 105, Japan, Fall 1981, pp. 149-183.

- [8] Tonoe, M., Preston, K., and Rosenfeld, A. (Editors), Real-Time/Parallel Computing: Image Analysis, Plenum Press, N.Y. 1981.

- [9] Duff, M. J. and Levialdi, S. (Editors), Languages and Architectures for Image Processing, Academic Press, N. Y., 1981.

- [10] Chang, N. S. and Fu, K. S., "Picture Query Languages for Pictorial Database Systems, " IEEE Computer Magazine, Nov. 1981, pp.23-33.

- [11] Chang, S. K. and Kunii, T. L., "Pictorial Database Systems," IEEE Computer Magazine, Nov. 1981, pp.13-22.

- [12] Hwang, K. and Su, S. P., "VLSI Matrix Manipulators for Feature Extraction and Pattern Classification," TR-EE81- , School of E. E., Purdue Univ., Lafayette, Indiana (submitted for publication).

- [13] Yang, T. Y. and Liu, P. S., "VLSI Arrays and Control Structure for Image Processing, "in Proc. Workshop Comp. Arch. For PAIDM, Hot Springs, 1981, pp.257-264.

- [14] Chu, K. H. and Fu, K. S., "VLSI Architectures for High-Speed Recognition of General Context-Free Languages and Finite-State Languages," TR-EE 81-42, Purdue University, 1981. (Submitted for publication).

- [15] Barnes, G. H., Brown, R. M., Kato, M., Kuck, D. J., and Stokes, R. W., "The Illiac IV Computer," TEEE Trans. Computers, Vol.C-17, 1968, pp.746-

- [16] Rohrbacher, D. and Potter, J.-L., "Image Processing with STARAN Parallel Computer," TEEE Computer Magazine, August 1977, pp. 54-59.

- [17] Duff, M. J. B., "Review of the CLIP Image Processing System," Proc. of NCC, Vol.47, AFIPS Press, 1978, pp.1055-1060.

- [18] Batcher, K. E., "Design of a Massively Parallel Processor," IEEE Trans. Computers, Vol.C-29, Setp. 1980, pp.836-840.

- [19] Hord, R. M. and Stevenson, D. K., "The Illiac IV Architecture and Its Sutiability For Image Processing," in Special Computer Architecture for Pattern Recognition, (Fu and Ichikawa, Editors), Chap.6, CRC Press, 1982, pp.

- [20] Faiss, R. J., Quinn, E. M., and Ruben, S., "Application of A Parallel Processing Computer in LACIE," Proc. 1976 Int'l Conf. Parallel Processing, pp. 24-32.

- [21] Potter, J. L., "Pattern Processing on STARAN," in Special Computer Architecture for Pattern Recognition, (Fu and Ichikawa, Editors), Chap. 5, CRC Press, 1982, pp.

- [22] Duff, M. J., "CLIP 4," in Special Computer Architecture for Pattern Recognition, (Fu and Ichikawa, Editors), Chap.4, CRC Press, 1982, pp.

- [23] Potter, J. L., "Image Processing on The Massively Parallel Processor", This issue.

- [24] Lougheed, R. M., McCubbrey, D. L., and Sternberg, S. R., "Cytocomputers: Architectures for Parallel Image Processing," Proc. Workshop Picture Data Description and Management, August 1980, pp.281-286.

- [25] Grandlund, G. H., et al., "The GOP IMage Processor," Proc.

Workshop Comp. Arch. for Pattern Analysis and Image Database

Management, IEEE Computer Society, 1981, pp.195-200.

- [26] Yen, D. W. L., and Kulkami, A..V., "The ESL Systolic Processor for Signal and Image Processing," Proc. Workshop.Comp. Arch. for PAIDM, Hot Springs, Virginia, 1981, pp. 265-272.

- [27] Sternberg, S. R., "Cytocomputers and Biomedical Image Processing", This issue.

- [28] Kung, H. T. and Leiserson, "Systolic Arrays (for VLSI)," in Sparse Matrix Proc. (Duff and Stewart, Eds), 1979, pp.256-28:

- [29] Kung, H. T. and Picard, R. L., "Hardware Pipelines for Multi-Dimensional Convolution and Resampling," Proc. Workshop Comp. Arch. for PAIDM, Hot Springs, 1981, pp.273-278.

- [30] Antonsson, D., et al., "PICAP A System Approach to Image Processing," Proc. Workshop Comp. Arch. for PAIDM, Hot Springs, Virginia, 1981, pp\_35-42.

- [31] Mori, K. I., Kidode, M., and Shinoda, H., and Asada, H., "Design of Local Parallel Pattern Processor for Image Processing," Proc. of NCC, Vol.47, AFIPS Press, 1978, pp.1025-1031.

- [32] Rieger, C., "ZMOB: Doing It in Parallel," in Proc. Workshop Comp. Arch. for PAIDM, Hot Springs, Virginia, 1981, pp.119-124.

- [33] Luetjen, K., Gemmar, P., and Ischen, H., "Flip: A Flexible Multiprocessor System for Image Processing," Proc. 5th Int'l Conf. Pattern Recognition, Miami Beach, Fla., 1980, pp.326-328.

- [34] Kushner, T., Wu, A. Y. and Rosenfeld, A., "Image Processing on ZMOB," Proc. Workshop Comp. Arch. for PAIDM, Hot Springs, 1981, pp.88-95.

- [35] Yamamura, M., Kamibayashi, N., and Ichikawa, T., "Organization of An Image Database Manipulation System," Proc. Workshop Comp. Arch. for PAIDM, Hot Springs, 1981, pp.236-241.

- [36] Zobrist, A. L. and Nagy, G., "Pictorial Information Processing of Landsat Data for Geographic Analysis", Computer, IEEE Computer Society, Nov. 1981, pp. 34-41.

- [37] Chock, M., Carderas, A. F., and Klinger, A., "Manipulating Data Structures in Pictorial Information Systems", Computer, IEEE Computer Society, Nov. 1981, pp. 43-50.

- [38] Wah, B. W. and Yao, S. B., "DIALOG A Distributed Processor Organization for Database Machine," Proc. of NCC, Vol.49, AFIPS Press, 1980, pp.243-253.

- [39] Hurson, A., "An Associative Backend Machine for Database Management," Proc. Workshop Comp. Arch. for PAIDM, Hot Springs, Virginia, 1981, pp.225-230.

- [40]Chang, N. S. and Yuan, Y. C., "VLSI Design and Verification of a Signal Processing Chip," Proc. Workshop Comp. ARch. for PAIDM, Hot Springs, 1981, pp.279-283.

- [41] Swartzlander, E., "VLSI Architecture," in VLSI: Fundamentals and Applications, (Barbe, Ed.) Springer Verlag, N. Y., 1980.

- [42] Preston, K., Duff, M. J., Levialdi, S., Norgren, P. E., and Toriwaki, J. I., "Basis of Cellular Logic With Some Applications in Medical Image Processing," IEEE Proceedings, Vol.67, May 1979, pp.826-856.

- [43] Hwang, K. and Cheng, Y. H. "Partitioned Matrix Computations for VLSI Arithmetic Systems", accepted to appear IEEE Transactions on Computer, 1982.

- [44] Foley, D. H. and Sammon, J. W., "An Optimal Set of Discrimiant Vectors," IEEE Trans. Computer, March 1975, pp.281-289.

- [45] Fu, K. S., Syntactic Methods in Pattern Recognition, Academic Press, N. Y., 1974.

- [46] DeWitt, T., "DIRECT: A Multiprocessor Database Machines," IEEE Trans. Computers, 1977.

- [47] Hwang, K., Computer Arithmetic: Principles, Architecture, and Design, John Wiley, 1979.

- [48] Fu, K. S., Syntatic Pattern Recognition and Applications, Prentice-Hall, Englewood Cliffs, N. J., 1981.

- [49] Fukunaga, K. Introduction To Statistical Pattern Recognition, Academic Press, N. Y. 1972.

- [50] Kidode, M., "Pattern Recognition Machines in Japan", This issue.

- [51] Rosenfeld, A., "Cellular Architectures For Pattern Recognition", This issue.

- [52] Briggs, F. A., M. Dubois, and K. Hwang, "Throughput Analysis and Configuration Design of A Shared-Resource Multiprocessor System: PUMPS", Proc. of 8th Annual Symposium on Computer Architecture, IEEE Computer Society, May 1981, pp. 67-80.

- [53] Tomlinson, R. "A Geographic Information System For Regional Planning", in <u>Land Evaluation</u>, (Ed. by Stewart), McMillan, Sydney, 1968.

- [54] Mantey, P. E. and Carlson, E. D., "Integrated Geographic Data Bases: The GADS Experience", in <u>Data Base Techniques for Pictorial Applications</u>, (Ed. by Blaser), Springer-Verlag, 1979, pp. 173-198.

- [55] McKeown, D. M. and Reddy, D. J., "A Hierarchical Symbolic Representation for Image Databases", <u>Proc. IEEE Workshop Picture Data Description and Management</u>, April 1977, pp. 40-44.

- [56] Berman, R. and Stonebraker, "GEO-QUEL: A System for The Manipulation and Display of Geographic Data", Computer Graphics, Vol. 11, No. 2, 1977, pp. 186-191.

- [57] Chang, S. K., Reuss, J. and McCormick, "Design Considerations of a Pictorial Database System", <u>Int'l Journal of Policy Analysis and Information Systems</u>, Vol. 1, No. 2, Jan. 1978, pp. 49-70.

- [58] Kunii, T.L. and Harada, M. "SID: A System for Interactive Design", AFIPS Conf. Proc., 1980 NCC, May 1980, pp. 33-40.

- [59] Lien, Y. E. and Utter, D. F., "Design of an Image Database", Proc. IEEE Workshop Picture Data Description and Management, April 1977, pp. 131-136.

- [60] Chrisman, N. and Little, J., "POLYVRT 1.1" Harvard University Int'l User's Conf. Computer Mapping Software and Databases, 1978.