# Class 7 Combinational Logic Functions

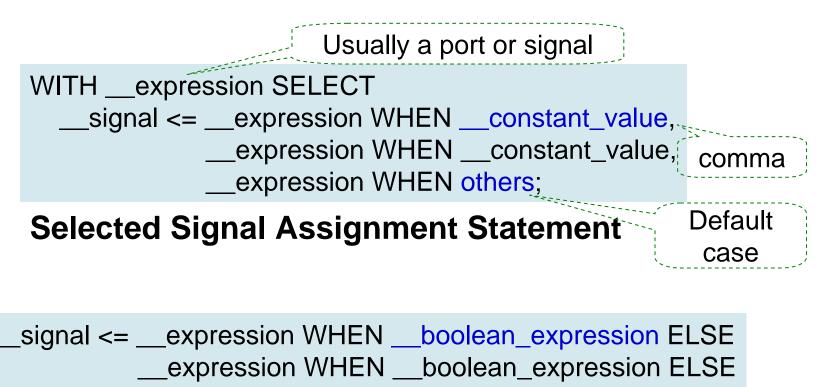

### Selected Signal Assignment Statement vs. Conditional Signal Assignment Statement

\_\_\_expression;-----

### **Conditional Signal Assignment Statement**

Can't be used in **PROCESS** statement

Copyright © All Rights Reserved by Yuan-Hao Chang

Default

case

END decoder:

### 2-Line-to-4-Line Decoder with an Enable Input

LIBRARY ieee; USE ieee.std\_logic\_1164.ALL; LIBRARY ieee: USE ieee.std\_logic\_1164.all; ENTITY decode IS PORT( ENTITY decode IS d: IN STD\_LOGIC\_VECTOR (1 downto 0); PORT( q: IN STD LOGIC; d: IN INTEGER Range 0 to 3; y: OUT STD\_LOGIC\_VECTOR (3 downto 0)); q: IN STD LOGIC; END decode; y: OUT STD\_LOGIC\_VECTOR (0 to 3)); END decode: ARCHITECTURE decoder OF decode IS SIGNAL inputs : STD\_LOGIC\_VECTOR (2 downto 0); ARCHITECTURE decoder OF decode IS **BEGIN** BEGIN  $inputs(2) \le g;$ Concatenate g (1 y <= "1000" WHEN (d=0 and g='0') ELSE inputs (1 downto 0)  $\leq d;$ bit) and d (2 bits) to "0100" WHEN (d=1 and g='0') ELSE WITH inputs SELECT "0010" WHEN (d=2 and g='0') ELSE get 3-bit vector v <= "0001" WHEN "000", "0001" WHEN (d=3 and g='0') ELSE "0010" WHEN "001". d(0) "0000": "0100" WHEN "010", END decoder ; "1000" WHEN "011", d(1) "0000" WHEN others;

g: enable

## **IF Statement**

IF \_\_\_boolean\_expression THEN \_\_\_statement;

```

_statement;

```

```

ELSIF ___boolean_expression THEN

```

\_\_statement;

```

_statement;

```

### ELSE

\_statement;

\_\_statement;

END IF;

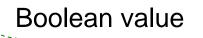

### **IF Statement**

IF(nRBI = '0' and input = "0000") THEN output <= "1111111"; -- 0 suppressed nRBO <= '0'; -- Next 0 suppressed ELSE nRBO <= '1'; -- Next 0 displayed END IF;

### Can be used in **PROCESS** statement

## **CASE Statement**

Usually a port or signal

CASE \_\_expression IS WHEN constant value => statement; statement; WHEN \_\_\_constant\_value => statement; \_\_\_\_statement; WHEN others => \_statement; statement;

END CASE;

### **CASE Statement**

Can be used in **PROCESS** statement

CASE input IS WHEN "0000" => output <= "0000001"; -- 0 displayed WHEN "0001" => "1001111"; -- 1 output <= WHEN "0010" => "0010010"; -- 2 output <= WHEN "0011" => "0000110"; -- 3 output <= WHEN "0100" => "1001100"; -- 4 output <= WHEN "0101" => "0100100"; -- 5 output <= WHEN "0110" => "1100000"; -- 6 output <= WHEN "0111" => output <= "0001111"; -- 7 WHEN "1000" => output <= "0000000"; -- 8 WHEN "1001" => "0001100"; -- 9 output <= WHEN others => "1111111"; -- blank output <= END CASE;

### PROCESS

- VHDL syntax requires an IF statement or a CASE statement to be contained within a PROCESS.

- IF statement and CASE statement can only be used in PROCESS statement

- A PROCESS is a construct containing statements that are executed if a signal in the sensitivity list of the PROCESS changes.

- A PROCESS statement is *concurrent*, but the statements inside the PROCESS are *sequential*.

PROCESS (nRBI, input)

| 1551 |

|------|

|------|

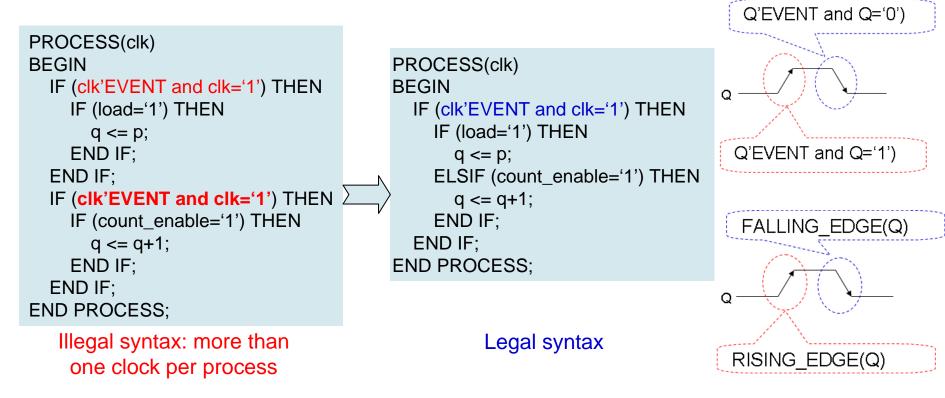

### **Possible Design Errors in PROCESS (Cont.)**

Only one instance of the EVENT express (e.g., clk'EVENT and clk='1') is allowed in a PROCESS statement.

### **Possible Design Errors in PROCESS (Cont.)**

• No other port, signal, or variable is allowed to be included with the expression that evaluates the clock.

```

PROCESS(clk)

BEGIN

IF (clk'EVENT and clk='1' and load='1') THEN

q \le p;

ELSE

q \le q+1;

END IF;

END PROCESS;

```

Illegal syntax: load evaluated in same statement as clk

```

PROCESS(clk)

BEGIN

IF (clk'EVENT and clk='1') THEN

IF (load='1') THEN

q <= p;

ELSE

q <= q+1;

END IF;

END IF;

END PROCESS;

```

#### Legal syntax

8

### **Possible Design Errors in PROCESS (Cont.)**

The statements in a process should be such that it is only possible to assign one value to a port, variable, or signal for each time the process executes.

```

PROCESS(clk)

BEGIN

IF (clk'EVENT and clk='1') THEN

IF (count_enable = '1') THEN

\begin{cases} q \le q+1; \\ END IF; \\ IF (load = '1') THEN \\ q \le p; \\ END IF; \\ IF (clear = '0') THEN \\ q \le (others =>'0'); \\ END IF; \\ END IF; \\ END IF; \\ END IF; \\ END PROCESS; \end{cases}

```

Ambigous (but not illegal) syntax: q assigned more than once in a process. May have an unexpected result.

```

\label{eq:process} \begin{array}{l} \mathsf{PROCESS}(\mathsf{clk}) \\ \mathsf{BEGIN} \\ \mathsf{IF}(\mathsf{clk'EVENT} \ \mathsf{and} \ \mathsf{clk=`1'}) \ \mathsf{THEN} \\ \left\{ \begin{array}{l} \mathsf{IF}(\mathsf{count\_enable}=`1') \ \mathsf{THEN} \\ \mathsf{q} <= \mathsf{q+1}; \\ \mathsf{ELSIF}(\mathsf{load}=`1') \ \mathsf{THEN} \\ \mathsf{q} <= \mathsf{p}; \\ \mathsf{ELSIF}(\mathsf{clear}=`0') \ \mathsf{THEN} \\ \mathsf{q} <= (\mathsf{others}=>`0'); \\ \mathsf{END} \ \mathsf{IF}; \\ \mathsf{END} \ \mathsf{IF}; \\ \mathsf{END} \ \mathsf{PROCESS}; \end{array} \right.

```

Legal syntax

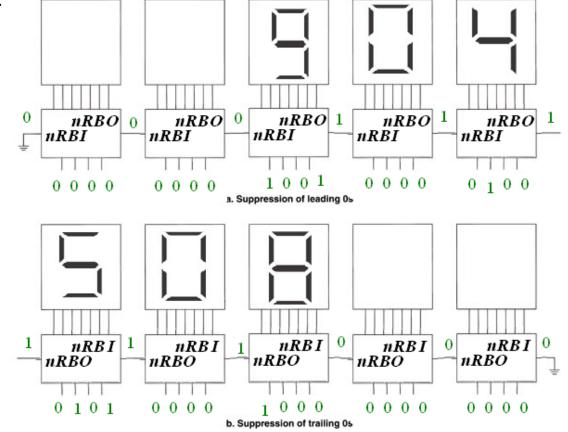

## **Ripple Blanking**

- A technique used in a multipledigit numerical display that suppresses leading or trailing zeros in the display, but allows internal zeros to be displayed.

- nRBI=0 and D=0

- $\rightarrow$  7-segment blank

- $\rightarrow$  nRBO=0

- otherwise

- $\rightarrow$  show digit

- → nRBO=1

- Suppress leading zeros

- Ground nRBI of the MSB digit

- Suppress trailing zeros

- Groud nRBI of the LSB digit

11

### **BCD-to-7Segment with Ripple Blanking**

ENTITY sevsegrb IS PORT( -- Use separate I/Os, not bus d3, d2, d1, d0: IN BIT;

nRBI: IN BIT :='0', -- set up the initial value

a, b, c, d, e, f, g, nRBO: OUT BIT);

END sevsegrb;

```

ARCHITECTURE seven_segment OF sevsegrb IS

-- Bit vectors for internal use

SIGNAL input: BIT_VECTOR (3 DOWNTO 0);

-- in decoder CASE statement

SIGNAL output: BIT VECTOR (6 DOWNTO 0);

BEGIN

-- Concatenate inputs to make bit vector

input <= d3 & d2 & d1 & d0;

-- Process Statement

assign_out: PROCESS (input, nRBI)

BEGIN

IF(nRBI = '0' and input = "0000") THEN

output <= "1111111"; -- 0 suppressed

nRBO <= '0'; -- Next 0 suppressed

ELSE

nRBO <= '1'; -- Next 0 displayed

```

**CASE** input IS WHEN "0000" => output <= "0000001"; -- 0 WHEN "0001" => output <= "1001111"; -- 1 WHEN "0010" => output <= "0010010"; -- 2 WHEN "0011" => output <= "0000110"; -- 3 WHEN "0100" => output <= "1001100": -- 4 WHEN "0101" => output <= "0100100"; -- 5 WHEN "0110" => output <= "1100000"; -- 6 WHEN "0111" => output <= "0001111"; -- 7 WHEN "1000" => output <= "0000000"; -- 8 WHEN "1001" => output <= "0001100"; -- 9 WHEN others => output <= "1111111"; -- blank END CASE: END IF: END PROCESS assign\_out;

-- pin outputs. a <= output(6); b <= output(5); c <= output(4); d <= output(3); e <= output(2); f <= output(1); g <= output(0); END seven segment;

ts Reserved by Yuan-Hao Chang

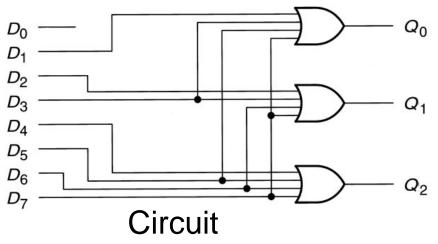

### **Encoders**

• 3-bit binary encoder

$$Q_{2} = D_{7} + D_{6} + D_{5} + D_{4}$$

$$Q_{1} = D_{7} + D_{6} + D_{3} + D_{2}$$

$$Q_{0} = D_{7} + D_{5} + D_{3} + D_{1}$$

Equation

Encoders might generate wrong codes: E.g., both D5 and D3 are on, the output of Q2Q1Q0 is 111.

### Truth Table

Copyright © All Rights Reserved by Yuan-Hao Chang

## **Priority Encoder**

- An encoder makes the output corresponding to the highestpriority input.

- Step 1: A bit goes HIGH if it is part of the code for an active input.

- Step 2: A bit goes LOW if it is a LOW of an input with a higher priority

- Development steps:

| Step 1 | $Q_{2} = D_{7} + D_{6} + D_{5} + D_{4}$ $Q_{1} = D_{7} + D_{6} + D_{3} + D_{2}$ $Q_{0} = D_{7} + D_{5} + D_{3} + D_{1}$                                                                                                                                                                            |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Step 2 | $Q_{2} = D_{7} + \overline{D_{6}} + D_{5} + D_{4}$ $Q_{1} = D_{7} + D_{6} + \overline{D_{5}}\overline{D_{4}}D_{3} + \overline{D_{5}}\overline{D_{4}}D_{2}$ $Q_{0} = D_{7} + \overline{D_{6}}D_{5} + \overline{D_{6}}\overline{D_{4}}D_{3} + \overline{D_{6}}\overline{D_{4}}\overline{D_{2}}D_{1}$ |

| $D_7$       | $D_6$ | $D_5$ | $D_4$ | $D_3$ | $D_2$ | $D_1$ | $D_0$ | $Q_2$ | $Q_1$ | $Q_0$ |

|-------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| 0           | 0     | 0     | 0     | 0     | 0     | 0     | Х     | 0     | 0     | 0     |

| 0           | 0     | 0     | 0     | 0     | 0     | 1     | Х     | 0     | 0     | 1     |

| 0           | 0     | 0     | 0     | 0     | 1     | Х     | Х     | 0     | 1     | 0     |

| 0           | 0     | 0     | 0     | 1     | Х     | Х     | Х     | 0     | 1     | 1     |

| 0           | 0     | 0     | 1     | Х     | Х     | Х     | Х     | 1     | 0     | 0     |

| 0           | 0     | 1     | Х     | Х     | Х     | Х     | Х     | 1     | 0     | 1     |

| 0           | 1     | Х     | Х     | Х     | Х     | Х     | Х     | 1     | 1     | 0     |

| 1           | Х     | Х     | Х     | Х     | Х     | Х     | Х     | 1     | 1     | 1     |

| Truth Table |       |       |       |       |       |       |       |       |       |       |

$\label{eq:copyright} @ \mbox{All Rights Reserved by Yuan-Hao Chang} \\$

14

## **Priority Encoder (Cont.)**

```

-- hi_pri8a.vhd

-- hi_pri8b.vhd

ENTITY hi_pri8a IS

ENTITY hi_pri8b IS

PORT(

PORT(

d: IN BIT_VECTOR(7 downto 0);

d: IN BIT_VECTOR(7 downto 0);

q: OUT BIT_VECTOR (2 downto 0));

q: OUT INTEGER RANGE 0 to 7);

END hi pri8a;

END hi pri8b;

ARCHITECTURE a OF hi_pri8a IS

ARCHITECTURE a OF hi_pri8b IS

BEGIN

BEGIN

-- Concurrent Signal Assignments

-- Conditional Signal Assignment

q <= 7 WHEN d(7)='1' ELSE

q(2) \le d(7) or d(6) or d(5) or d(4);

6 WHEN d(6)='1' ELSE

5 WHEN d(5)='1' ELSE

q(1) \le d(7) or d(6)

or ((not d(5)) and (not d(4)) and d(3))

4 WHEN d(4)='1' ELSE

or ((not d(5)) and (not d(4)) and d(2));

3 WHEN d(3)='1' ELSE

2 WHEN d(2)='1' ELSE

1 WHEN d(1)='1' ELSE

q(0) \le d(7) or ((not d(6)) and d(5))

or ((not d(6))) and (not d(4)) and d(3))

0:

or ((not d(6)) and (not d(4)) and (not d(2)) and d(1));

END a;

END a:

```

Copyright © All Rights Reserved by Yuan-Hao Chang

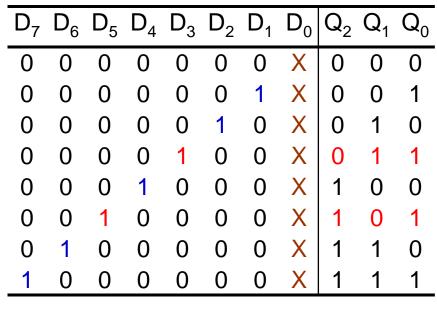

## Lab 7

- Part 1: Design a BCD priority Encoder. (7-segment shows 0~9)

- The 7-segment shows the number corresponding to the switch that is ON and has the highest priority, where a switch with the larger numeric value has higher priority.

- If all of the switches are OFF, turn off the 7-segment LED.

- Part 2: Design a 3-digit octal-to-7segment decoder with the leading zeros suppressed, as follow:

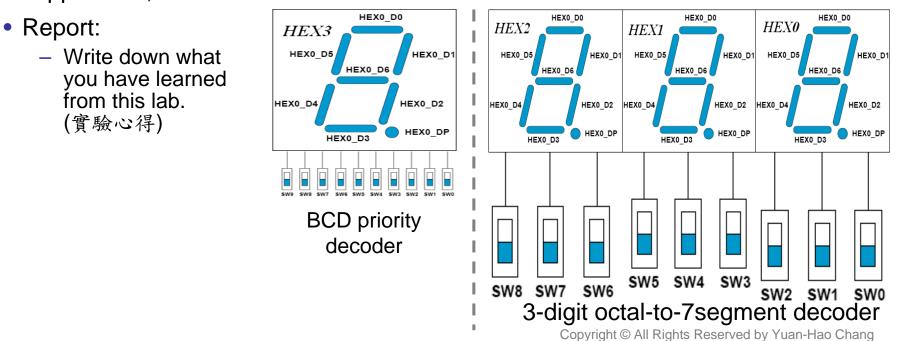

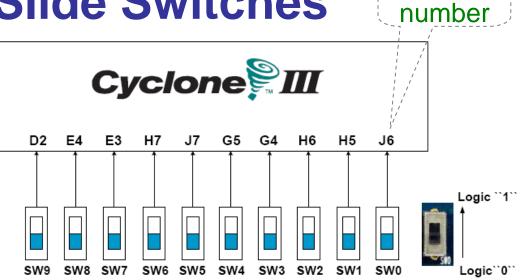

### **Pushbutton and Slide Switches**

3 Pushbutton switches: Not pressed  $\rightarrow$  Logic High Pressed  $\rightarrow$  Logic Low

| Signal Name | FPGA Pin No. |

|-------------|--------------|

| BUTTON [0]  | PIN_ H2      |

| BUTTON [1]  | PIN_G3       |

| BUTTON [2]  | PIN_F1       |

### 10 Slide switches (Sliders): Up $\rightarrow$ Logic High Down $\rightarrow$ Logic

|       | -      |       |        |

|-------|--------|-------|--------|

| SW[0] | PIN_J6 | SW[5] | PIN_J7 |

| SW[1] | PIN_H5 | SW[6] | PIN_H7 |

| SW[2] | PIN_H6 | SW[7] | PIN_E3 |

| SW[3] | PIN_G4 | SW[8] | PIN_E4 |

| SW[4] | PIN_G5 | SW[9] | PIN_D2 |

Pin

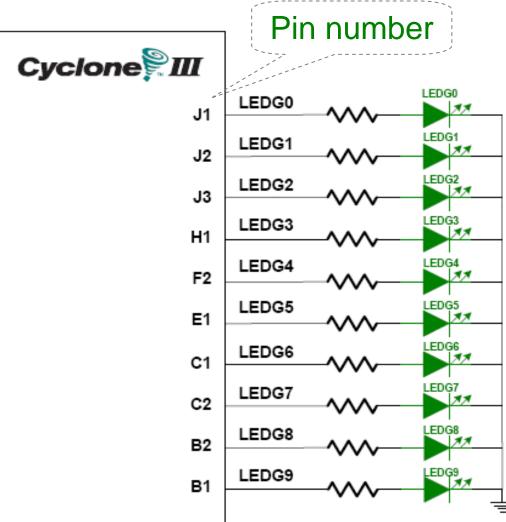

**LEDs**

### 10 LEDs Opuput high $\rightarrow$ LED on Output low $\rightarrow$ LED off

| Signal Name | FPGA Pin No. |

|-------------|--------------|

| LEDG[0]     | PIN_J1       |

| LEDG[1]     | PIN_J2       |

| LEDG[2]     | PIN_J3       |

| LEDG[3]     | PIN_H1       |

| LEDG[4]     | PIN_F2       |

| LEDG[5]     | PIN_E1       |

| LEDG[6]     | PIN_C1       |

| LEDG[7]     | PIN_C2       |

| LEDG[8]     | PIN_B2       |

| LEDG[9]     | PIN_B1       |

Copyright © All Rights Reserved by Yuan-Hao Chang

Pin number

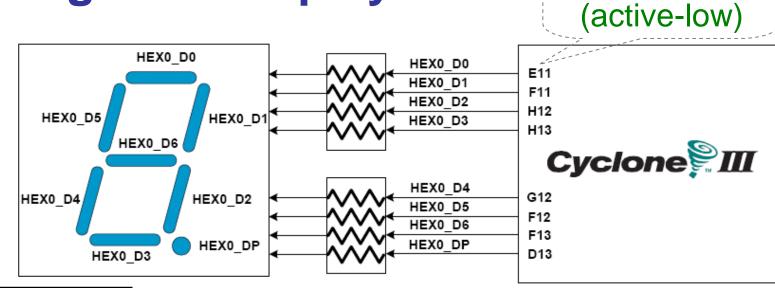

## **7-Segment Displays**

| Signal Name | FPGA Pin No. |           |         |   |           |                |           |         |

|-------------|--------------|-----------|---------|---|-----------|----------------|-----------|---------|

| HEX0_D[0]   | PIN_E11      | HEX1_D[0] | PIN_A13 |   | HEX2_D[0] | PIN_D15        | HEX3_D[0] | PIN_B18 |

| HEX0_D[1]   | PIN_F11      | HEX1_D[1] | PIN_B13 |   | HEX2_D[1] | PIN_A16        | HEX3_D[1] | PIN_F15 |

| HEX0_D[2]   | PIN_H12      | HEX1_D[2] | PIN_C13 |   | HEX2_D[2] | PIN_B16        | HEX3_D[2] | PIN_A19 |

| HEX0_D[3]   | PIN_H13      | HEX1_D[3] | PIN_A14 |   | HEX2_D[3] | PIN_E15        | HEX3_D[3] | PIN_B19 |

| HEX0_D[4]   | PIN_G12      | HEX1_D[4] | PIN_B14 |   | HEX2_D[4] | PIN_A17        | HEX3_D[4] | PIN_C19 |

| HEX0_D[5]   | PIN_F12      | HEX1_D[5] | PIN_E14 |   | HEX2_D[5] | PIN_B17        | HEX3_D[5] | PIN_D19 |

| HEX0_D[6]   | PIN_F13      | HEX1_D[6] | PIN_A15 |   | HEX2_D[6] | PIN_F14        | HEX3_D[6] | PIN_G15 |

| HEX0_DP     | PIN_D13      | HEX1_DP   | PIN_B15 | • | HEX2_DP   | PIN_A18 Rights | HEX3_DP   | PIN_G16 |