# Class 8 MUX / DMUX and Full Adder

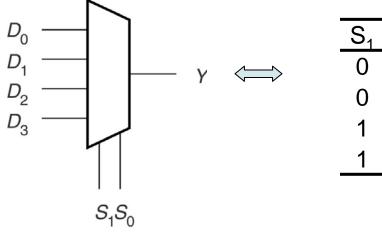

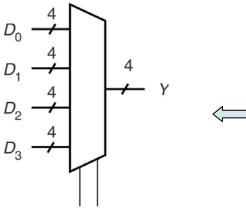

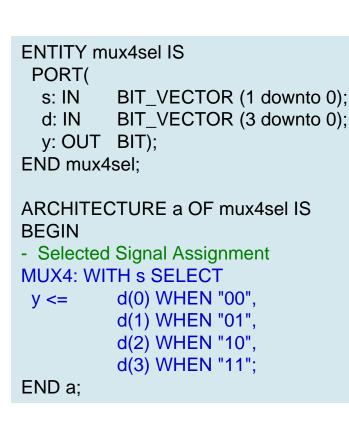

### **Multiplexer (MUX)**

$S_{1}S_{0}$

| <b>S</b> <sub>1</sub> | $S_0$ | $Y_3$           | $Y_2$           | Y <sub>1</sub>         | $Y_0$                                                                    |

|-----------------------|-------|-----------------|-----------------|------------------------|--------------------------------------------------------------------------|

| 0                     | 0     | D <sub>03</sub> | D <sub>02</sub> | <b>D</b> <sub>01</sub> | D <sub>00</sub><br>D <sub>10</sub><br>D <sub>20</sub><br>D <sub>30</sub> |

| 0                     | 1     | D <sub>13</sub> | $D_{12}$        | D <sub>11</sub>        | D <sub>10</sub>                                                          |

| 1                     | 0     | D <sub>23</sub> | D <sub>22</sub> | $D_{21}$               | $D_{20}$                                                                 |

| 1                     | 1     | D <sub>33</sub> | $D_{32}$        | D <sub>31</sub>        | D <sub>30</sub>                                                          |

$S_0$

0

1

0

1

1

1

Y

$\mathsf{D}_0$

$D_1$

$D_2$

$D_3$

## Multiplexer (MUX)

ENTITY mux4case IS PORT( d0, d1, d2, d3: IN BIT; -- data inputs s: IN BIT VECTOR (1 downto 0); -- select inputs y: OUT BIT); END mux4case:

ARCHITECTURE mux4to1 OF mux4case IS **BEGIN**

-- Monitor select inputs and execute if they change PROCESS(s)

```

BEGIN

```

CASE s IS WHEN "00"

WHEN "01"

WHEN "10"

WHEN "11"

END CASE;

END mux4to1:

END PROCESS:

WHEN others

- y <= d0;=> => y <= d1; => y <= d2; => y <= d3;

- v <= '0': =>

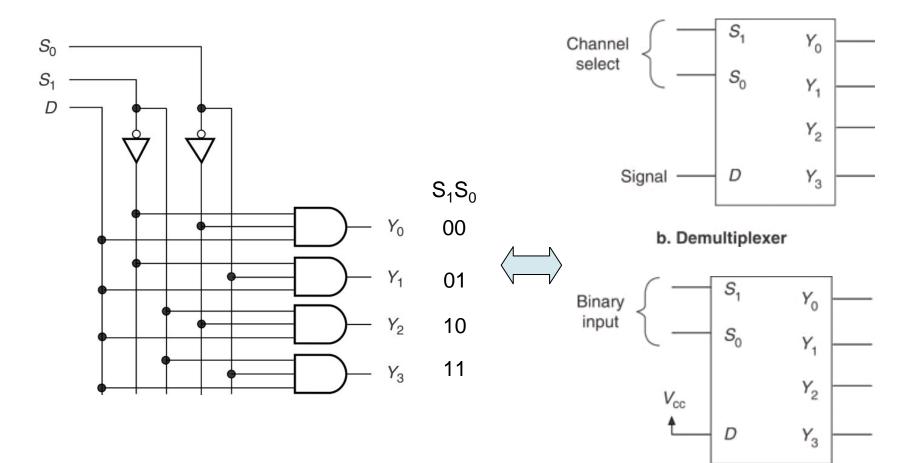

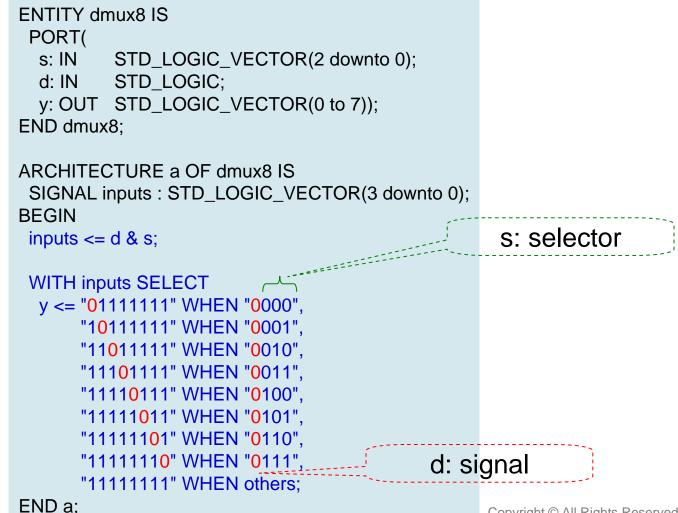

### **Demultiplexer (DMUX)**

### **Demultiplexer (DMUX) (Cont.)**

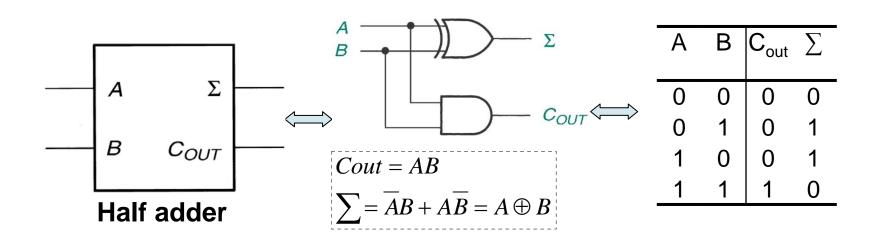

#### Half Adder

6

December 21, 2010 ABCIN 0 1 1 **Full Adder** 00 1 00 0 0 0 Σ Α 1 01 1 01 0 0  $C_{IN} C_{out} \Sigma$ Can't simplify  $\Sigma$ Α В by K-map В 1 11 11 1 1 0 0 0 0 0 0 10 0 10 1 0  $C_{IN}$  $C_{OUT}$ 0 0 1 0 1 COUT Σ 0 1 0 0 1  $A \oplus B$ А 0 0 1 1  $\Sigma = (A \oplus B) \oplus C_{IN}$ В 0 1 0 1 0 (A ⊕ B) CIN 0 AB 0 1 1 1 0 0 CIN - COUT  $Cout = \overline{ABC} + A\overline{BC} + AB\overline{C} + AB\overline{C}$ = (A

B) CIN + AB =(AB+AB)C+AB(C+C)Half adder Half adder  $= (A \oplus B)C + AB$  $A \oplus B$  $(A \oplus B) \oplus C_{IN}$ Σ A Σ Α А  $\sum = \overline{ABC} + ABC + \overline{ABC} + A\overline{BC}$ В В В (A ⊕ B) CIN AB COUT COUT =(AB+AB)C+(AB+AB)C

CIN

$= (A \oplus B)C + (A \oplus B)C$  $= (A \oplus B) \oplus C$

$= (A \oplus B) C_{IN} + AB$

COUT

7

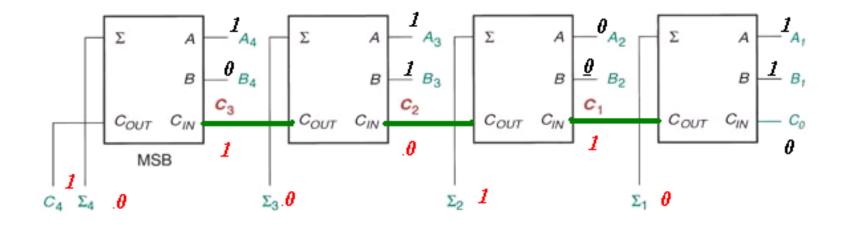

#### Parallel Binary Adder (Ripple Carry Binary Adder)

$A_4 A_3 A_2 A_1 = 1101$  $B_4 B_3 B_2 B_1 = 0101$ A + B = 10010

9

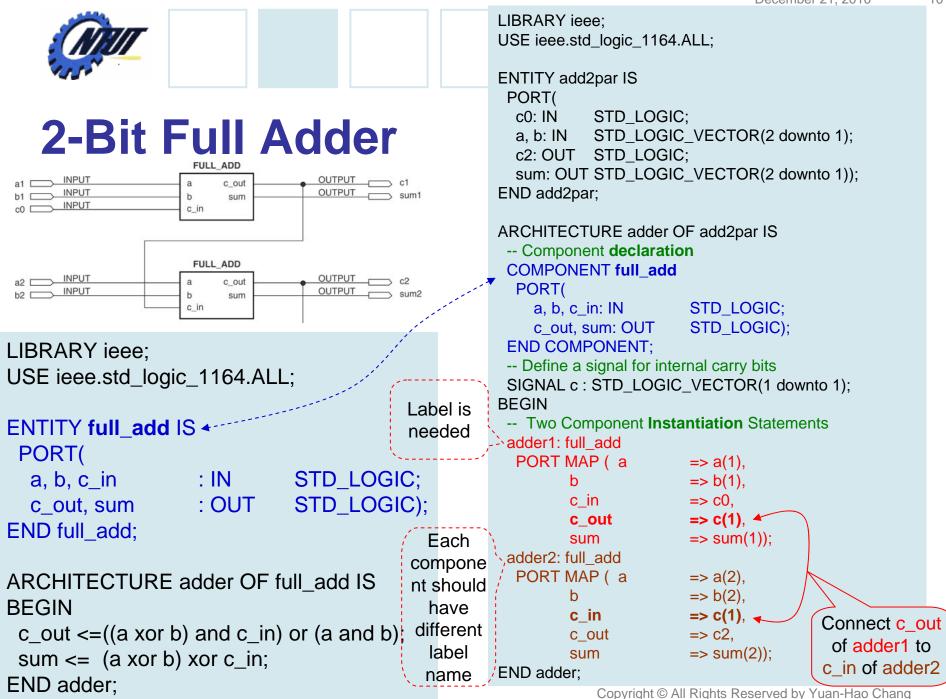

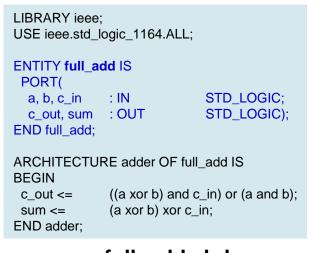

LIBRARY ieee; USE ieee.std\_logic\_1164.ALL;

```

ENTITY full_add IS

PORT(

a, b, c_in : IN STD_LOGIC;

c_out, sum : OUT STD_LOGIC);

END full_add;

```

```

ARCHITECTURE adder OF full_add IS

BEGIN

c_out <=((a xor b) and c_in) or (a and b);

sum <= (a xor b) xor c_in;

END adder;

```

$Cout = \overline{ABC} + A\overline{BC} + AB\overline{C} + ABC$  $= (\overline{AB} + A\overline{B})C + AB(\overline{C} + C)$  $= (A \oplus B)C + AB$  $\sum = \overline{ABC} + ABC + \overline{ABC} + A\overline{BC}$  $= (\overline{AB} + AB)C + (\overline{AB} + A\overline{B})\overline{C}$  $= (\overline{A \oplus B})C + (A \oplus B)\overline{C}$  $= ((A \oplus B) \oplus C)$

December 21, 2010

11

END adder;

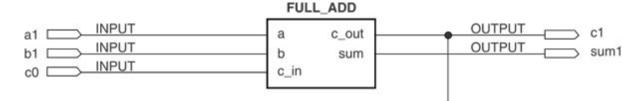

#### 2-Bit Full Adder (Cont.)

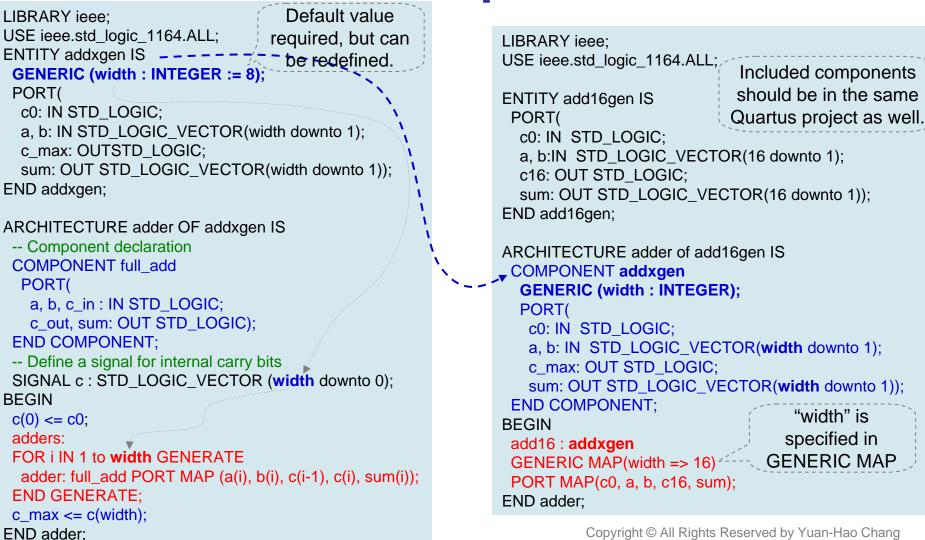

LIBRARY ieee; USE ieee.std\_logic\_1164.ALL; ENTITY add4gen IS PORT( c0: IN STD\_LOGIC; a, b: IN STD\_LOGIC\_VECTOR(2 downto 1); c2: OUT STD\_LOGIC; sum: OUT STD\_LOGIC\_VECTOR(2 downto 1)); END add4gen;

```

END add4gen;

ARCHITECTURE adder OF add4gen IS

-- Component declaration

COMPONENT full add

BEGIN

PORT(a, b, c in: IN

STD_LOGIC;

c out, sum: OUT STD LOGIC);

adder1: full add

END COMPONENT;

PORT MAP ( a

-- Define a signal for internal carry bits

b

SIGNAL c : STD_LOGIC_VECTOR (2 downto 0);

c in

BEGIN

c_out

c(0) \le c(1), c(1

sum

adder2: full add

Label is needed

adders:

PORT MAP ( a

FOR i IN 1 to 2 GENERATE

b

adder: full_add PORT MAP (a(i), b(i), c(i-1), c(i), sum(i));

c_in

END GENERATE;

c_out

sum

adder2: full_add PORT MAP (a(2), b(2), c(1), c2, sum(2));

END adder:

c2 \le c(2)

```

LIBRARY ieee; USE ieee.std\_logic\_1164.ALL;

```

ENTITY add2par IS

PORT(

c0: IN

STD LOGIC:

a, b: IN

STD_LOGIC_VECTOR(2 downto 1);

c2: OUT STD LOGIC;

sum: OUT STD_LOGIC_VECTOR(2 downto 1));

END add2par;

ARCHITECTURE adder OF add2par IS

-- Component declaration

COMPONENT full_add

PORT(

STD LOGIC:

a, b, c in: IN

c out, sum: OUT

STD LOGIC);

END COMPONENT;

-- Define a signal for internal carry bits

SIGNAL c : STD_LOGIC_VECTOR(1 downto 1);

-- Two Component Instantiation Statements

=> a(1),

=> b(1),

=> c0,

=> c(1),

=> sum(1));

=> a(2),

=> b(2),

=> c(1),

=> c2,

=> sum(2));

```

### **Full Adder with Unspecified Width**

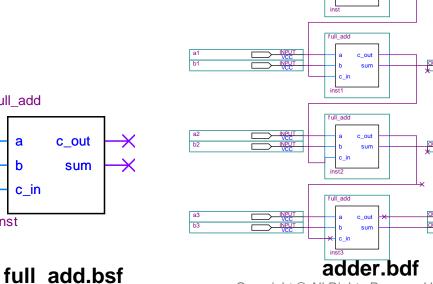

#### The Procedure to Import VHDL Code to **Block Diagram/Schematic File**

- The procedure to import a VHDL full-adder to a .bdf file to construct a four-bit full adder:

- 1. Create a guartus project with entity name "adder" \_

- 2. Create a new full\_add.vhd file and save it as a full\_add.bsf file. (File $\rightarrow$ Create/Update $\rightarrow$ Create Symbol File...)

- 3. Create a new adder.bdf file (the file name is its entity name) \_

full add

а

b

inst

c in

×

- 4. Incude full\_add.bsf file as a component into adder.bdf

- 5. Pin assignment to complete the design

full add.vhd

Copyright © All Rights Reserved by Yuan-Hao Chang

full add

$\rightarrow$  s<sup>2</sup>

⇒ sä

13

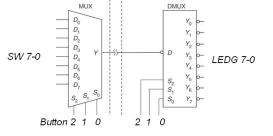

## Lab 8

#### Part 1: Design a MUX/DMUX

Use Button2-Button0 as the selectors to decide which slide switch among SW7-SW0 is selected to show its status on its corresponding LED. The LEDs that are not selected should be turned off. For example:

- When Button2 is pushed, the status of SW4 is shown on LEDG4.

When Button2 and Button0 are both pushed, the status of SW5 is shown on LEDG5.

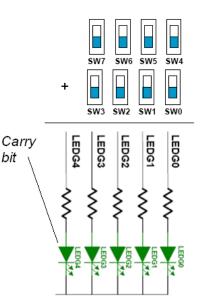

- Part 2: Full adder

- Implement a 4-bit full adder:

- SW7-4 is the first 4-bit operand, and SW3-0 is the second 4-bit operand.

- Please show the result on LEDs, where LEDG4 is the carry of the MSB bit, and LEDG3-0 are  $\sum$ 3-0, respectively.

- LED is on when the corresponding  $\Sigma$  bit is 1.

- Report:

- Write down what you have learned from this lab. (實驗心得)

14

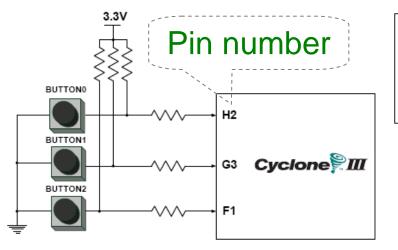

#### **Pushbutton and Slide Switches**

3 Pushbutton switches: Not pressed  $\rightarrow$  Logic High Pressed  $\rightarrow$  Logic Low

| Signal Name | FPGA Pin No. |  |  |

|-------------|--------------|--|--|

| BUTTON [0]  | PIN_H2       |  |  |

| BUTTON [1]  | PIN_G3       |  |  |

| BUTTON [2]  | PIN_F1       |  |  |

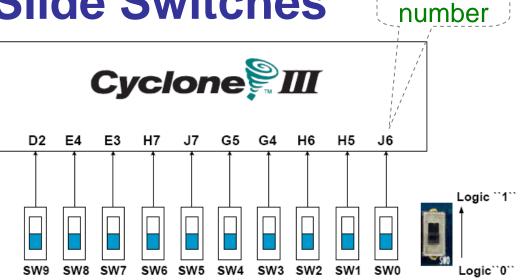

#### 10 Slide switches (Sliders): Up $\rightarrow$ Logic High Down $\rightarrow$ Logic

|       |       | -      |       |        |  |

|-------|-------|--------|-------|--------|--|

| SW[0] |       | PIN_J6 | SW[5] | PIN_J7 |  |

|       | SW[1] | PIN_H5 | SW[6] | PIN_H7 |  |

|       | SW[2] | PIN_H6 | SW[7] | PIN_E3 |  |

|       | SW[3] | PIN_G4 | SW[8] | PIN_E4 |  |

|       | SW[4] | PIN_G5 | SW[9] | PIN_D2 |  |

Pin

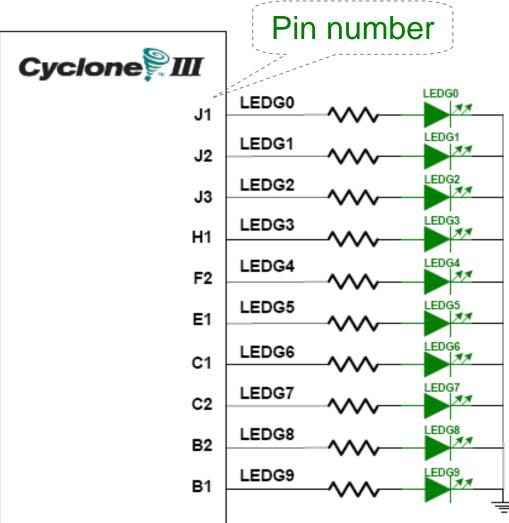

**LEDs**

#### 10 LEDs Opuput high $\rightarrow$ LED on Output low $\rightarrow$ LED off

| Signal Name | FPGA Pin No. |

|-------------|--------------|

| LEDG[0]     | PIN_J1       |

| LEDG[1]     | PIN_J2       |

| LEDG[2]     | PIN_J3       |

| LEDG[3]     | PIN_H1       |

| LEDG[4]     | PIN_F2       |

| LEDG[5]     | PIN_E1       |

| LEDG[6]     | PIN_C1       |

| LEDG[7]     | PIN_C2       |

| LEDG[8]     | PIN_B2       |

| LEDG[9]     | PIN_B1       |

Pin number

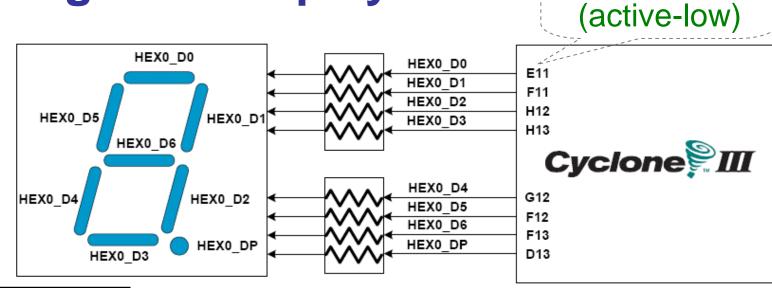

## **7-Segment Displays**

| Signal Name | FPGA Pin No. |           |         |           |                |           |         |

|-------------|--------------|-----------|---------|-----------|----------------|-----------|---------|

| HEX0_D[0]   | PIN_E11      | HEX1_D[0] | PIN_A13 | HEX2_D[0] | PIN_D15        | HEX3_D[0] | PIN_B18 |

| HEX0_D[1]   | PIN_F11      | HEX1_D[1] | PIN_B13 | HEX2_D[1] | PIN_A16        | HEX3_D[1] | PIN_F15 |

| HEX0_D[2]   | PIN_H12      | HEX1_D[2] | PIN_C13 | HEX2_D[2] | PIN_B16        | HEX3_D[2] | PIN_A19 |

| HEX0_D[3]   | PIN_H13      | HEX1_D[3] | PIN_A14 | HEX2_D[3] | PIN_E15        | HEX3_D[3] | PIN_B19 |

| HEX0_D[4]   | PIN_G12      | HEX1_D[4] | PIN_B14 | HEX2_D[4] | PIN_A17        | HEX3_D[4] | PIN_C19 |

| HEX0_D[5]   | PIN_F12      | HEX1_D[5] | PIN_E14 | HEX2_D[5] | PIN_B17        | HEX3_D[5] | PIN_D19 |

| HEX0_D[6]   | PIN_F13      | HEX1_D[6] | PIN_A15 | HEX2_D[6] | PIN_F14        | HEX3_D[6] | PIN_G15 |

| HEX0_DP     | PIN_D13      | HEX1_DP   | PIN_B15 | HEX2_DP   | PIN_A18 Rights | HEX3_DP   | PIN_G16 |