# Class 11 Shift Registers

January 11, 2011

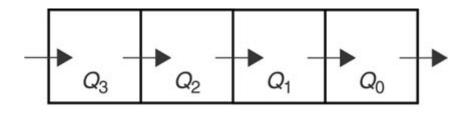

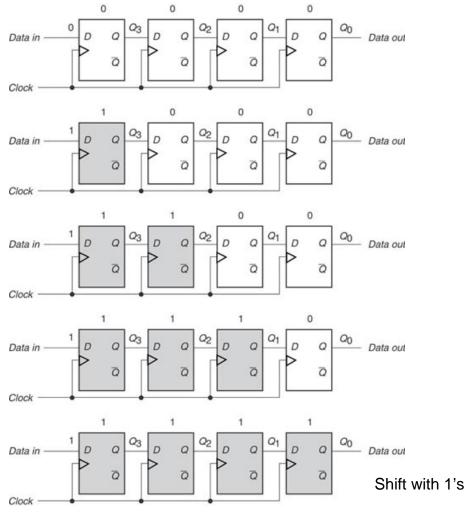

# **Serial Shift Register**

January 11, 2011

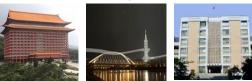

Shift a "1"

# Serial Shift Register (Cont.)

# **Universal Shift Register**

| <b>S</b> <sub>1</sub>     | S <sub>0</sub>             | Function    | $D_3$   | $D_2$ | D <sub>1</sub>   | D <sub>0</sub> |

|---------------------------|----------------------------|-------------|---------|-------|------------------|----------------|

| 0                         | 0                          | Hold        | $Q_3$   | $Q_2$ | Q <sub>1</sub>   | Q <sub>0</sub> |

| 0                         | 1                          | Shift Right | RSI     | $Q_3$ | $Q_2$            | $Q_1$          |

| 1                         | 0                          | Shift Left  | $Q_2$   | $Q_1$ | $\overline{Q_0}$ | LSI            |

| 1                         | 1                          | Load        | $P_3^-$ | $P_2$ | $P_1$            | $P_0$          |

| RSI: Right<br>LSI: Left-S | -Shift Input<br>hift Input |             |         |       |                  |                |

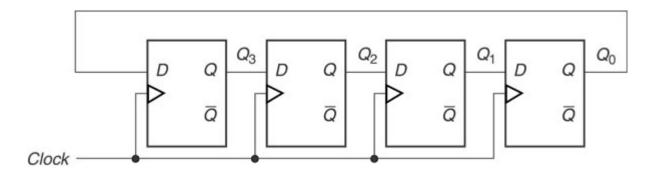

# **Ring Counter**

• A serial shift register with feedback from the output of the last flip-flop to the input of the first.

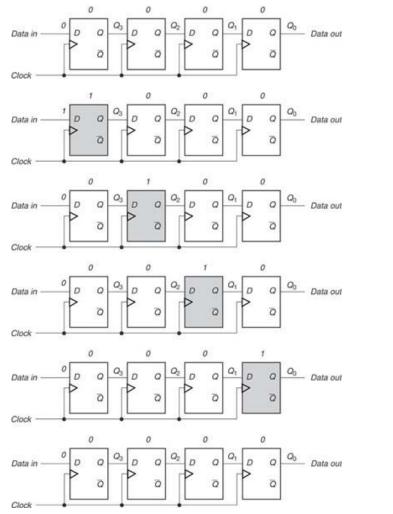

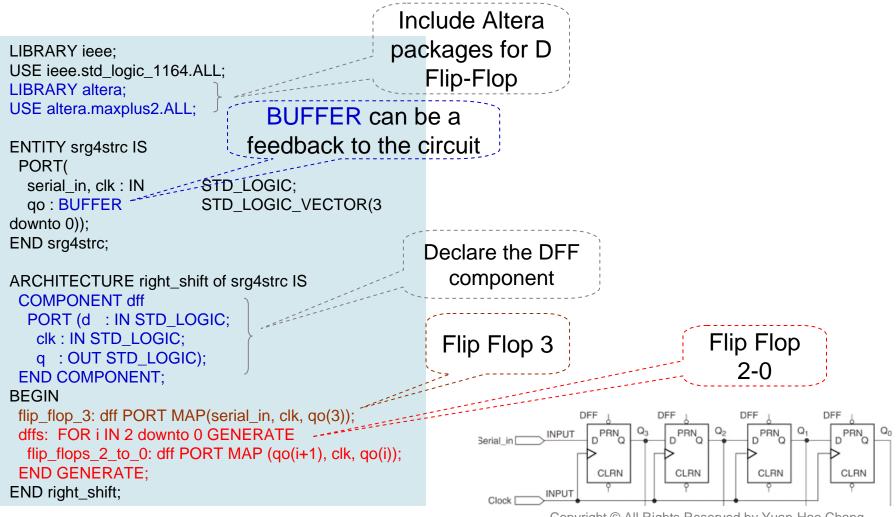

#### Shift Register – Structural Design

# Shift Register – Dataflow Design / Behavioral Design

LIBRARY ieee; USE ieee.std\_logic\_1164.ALL;

```

ENTITY srg4dflw IS

PORT(

serial_in, clk : IN STD_LOGIC;

q: BUFFER STD_LOGIC_VECTOR(3 downto 0));

END srg4dflw;

```

```

ARCHITECTURE right_shift OF srg4dflw IS

SIGNAL d : STD_LOGIC_VECTOR(3 downto 0);

BEGIN

PROCESS (clk)

BEGIN

-- Define a 4-bit D flip-flop

IF (clk'EVENT and clk = '1') THEN

q <= d;

END IF;

END PROCESS;

d <= serial_in & q(3 downto 1);

END right_shift;

```

Dataflow design: describe a design entity in terms of the Boolean relationships between different parts of the circuit.

LIBRARY ieee; USE ieee.std\_logic\_1164.ALL;

ENTITY srg4behv IS PORT( serial\_in, clk : IN STD\_LOGIC; END srg4behv;

```

ARCHITECTURE right_shift OF srg4behv IS

SIGNAL d : STD_LOGIC_VECTOR(3 downto 0);

BEGIN

PROCESS (clk)

BEGIN

-- Define a 4-bit D flip-flop

IF (clk'EVENT and clk = '1') THEN

q <= serial_in & q(3 downto 1);

END IF;

END PROCESS;

END right_shift;

```

### Behavioral design: describe a design entity in terms of the behavior of the circuit.

# **Shift Registers of Generic Width**

| Use the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                         |                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-------------------------------------------------------------------------------|

| GENERIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | LIBRARY ieee;                           | LIBRARY ieee;                                                                 |

| clause to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | USE ieee.std_logic_1164.ALL;            | USE ieee.std_logic_1164.ALL;                                                  |

| define a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                         | USE ieee.std_logic_arith.ALL;                                                 |

| barameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -ENTITY srg4dflw IS                     | USE ieee.std_logic_unsigned.ALL;                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | GENERIC (width: POSITIVE := 4)          | ENTITY srg4dflw IS                                                            |

| ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | PORT(                                   | GENERIC (width: POSITIVE := 4)                                                |

| Default                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | serial_in, clk, clear : IN STD_LOGIC;   | PORT(                                                                         |

| value is 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | q: BUFFER                               | serial_in, clk, clear : IN STD_LOGIC;                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | STD_LOGIC_VECTOR(width-1 downto 0));    | q: BUFFER                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | END srg4dflw;                           | STD_LOGIC_VECTOR(width-1 downto 0));                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         | END srg4dflw;                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ARCHITECTURE right_shift OF srg4dflw IS |                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | BEGIN                                   | ARCHITECTURE right_shift OF srg4dflw IS                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PROCESS (clk)<br>BEGIN                  | BEGIN                                                                         |

| 1 North Contraction of the second sec |                                         | PROCESS (clk)<br>BEGIN                                                        |

| Clear                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <pre>IF (clear = '0') THEN</pre>        |                                                                               |

| every bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ELSIF (clk'EVENT and clk = '1') THEN    | <pre>IF (clear = '0') THEN     q &lt;= CONV_STD_LOGIC_VECTOR(0, width);</pre> |

| of q() to '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $q \le d;$                              | ELSIF (clk'EVENT and clk = '1') THEN                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | END IF;                                 | $q \leq d;$                                                                   |

| · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | END PROCESS;                            | END IF;                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | d <= serial_in & q(width-1 downto 1);   | END PROCESS;                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | END right_shift;                        | d <= serial_in & q(width-1 downto 1);                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | •                                       | END right_shift;                                                              |

| <u>(NUT</u> |

|-------------|

| 1550        |

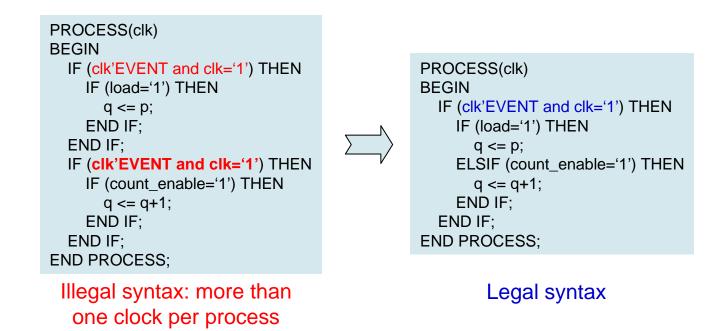

# **Possible Design Errors in PROCESS**

- In VHDL, a PROCESS statement is *concurrent*, but statements inside the PROCESS are sequential.

- Anything described by a PROCESS acts like a separate component in a design entity.

- Possible design errors:

- Only one instance of the EVENT express (e.g., clk'EVENT and clk='1') is allowed in a PROCESS statement.

- No other port, signal, or variable is allowed to be included with the expression that evaluates the clock.

- For the statements in a process, it is only possible to assign one value to a port, variable, or signal for each time the process executes.

### **Possible Design Errors in PROCESS (Cont.)**

Only one instance of the EVENT express (e.g., clk'EVENT and clk='1') is allowed in a PROCESS statement.

### **Possible Design Errors in PROCESS (Cont.)**

• No other port, signal, or variable is allowed to be included with the expression that evaluates the clock.

#### Legal syntax

| <b>ANT</b> |

|------------|

|            |

|            |

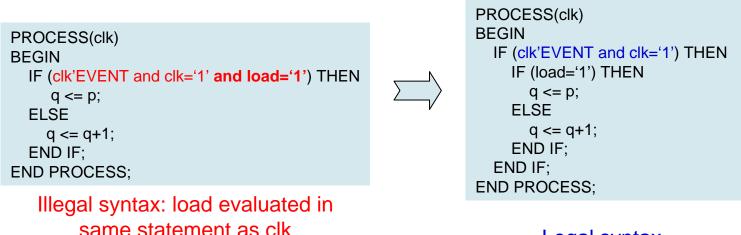

# **Possible Design Errors (Cont.)**

• For the statements in a process, it is only possible to assign one value to a port, variable, or signal for each time the process executes.

```

PROCESS(clk)

BEGIN

IF (clk'EVENT and clk='1') THEN

\begin{cases} IF (count_enable = '1') THEN \\ q <= q+1; \\ END IF; \\ IF (load = '1') THEN \\ q <= p; \\ END IF; \\ IF (clear = '0') THEN \\ q <= (others =>'0'); \\ END IF; \\ END IF; \\ END IF; \\ END IF; \\ END PROCESS; \end{cases}

```

Ambigous (but not illegal) syntax: q assigned more than once in a process. May have an unexpected result.

```

\begin{array}{l} \mathsf{PROCESS(clk)} \\ \mathsf{BEGIN} \\ \mathsf{IF} (\mathsf{clk'EVENT} \ \mathsf{and} \ \mathsf{clk='1'}) \ \mathsf{THEN} \\ \left\{ \begin{array}{l} \mathsf{IF} \ (\mathsf{count\_enable} = \ '1') \ \mathsf{THEN} \\ \mathsf{q} <= \mathsf{q+1}; \\ \mathsf{ELSIF} \ (\mathsf{load} = \ '1') \ \mathsf{THEN} \\ \mathsf{q} <= \mathsf{p}; \\ \mathsf{ELSIF} \ (\mathsf{load} = \ '1') \ \mathsf{THEN} \\ \mathsf{q} <= \mathsf{p}; \\ \mathsf{ELSIF} \ (\mathsf{clear} = \ '0') \ \mathsf{THEN} \\ \mathsf{q} <= (\mathsf{others} => \ '0'); \\ \mathsf{END} \ \mathsf{IF}; \\ \mathsf{END} \ \mathsf{IF}; \\ \mathsf{END} \ \mathsf{PROCESS}; \end{array} \right.

```

Legal syntax

# Lab 11

• Design a universal shift register with feedback from the output. The shift frequency is 5Hz.

| PB <sub>2</sub> | PB <sub>1</sub> | Function    | LED <sub>9</sub> | LED <sub>8</sub> | ••• | LED <sub>1</sub> | LED <sub>0</sub> |

|-----------------|-----------------|-------------|------------------|------------------|-----|------------------|------------------|

| 1               | 1               | Hold        | LED <sub>9</sub> | LED <sub>8</sub> |     | LED <sub>1</sub> | LED <sub>0</sub> |

| 1               | 0               | Shift Right | LED <sub>0</sub> | LED <sub>9</sub> |     | $LED_2$          | $LED_1$          |

| 0               | 1               | Shift Left  | $LED_8$          | $LED_7$          |     | LED <sub>0</sub> | $LED_9$          |

| 0               | 0               | Load        | SW <sub>9</sub>  | SW <sub>8</sub>  |     | SW <sub>1</sub>  | SW <sub>0</sub>  |

#### • Report:

- Write down what you have learned from this lab. (實驗心得)

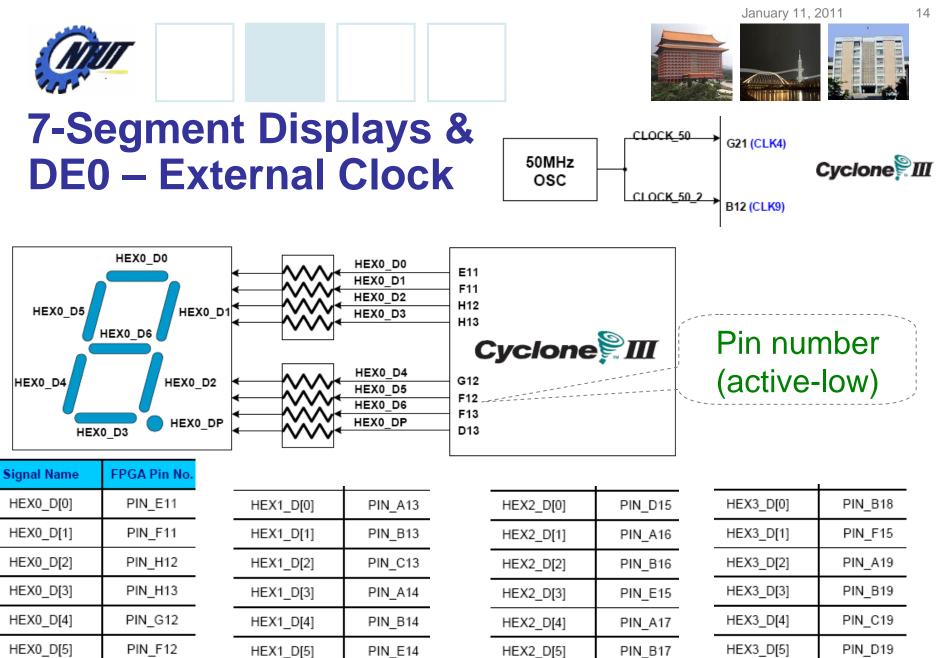

| HEX0_D[0] | PIN_E11 |

|-----------|---------|

| HEX0_D[1] | PIN_F11 |

| HEX0_D[2] | PIN_H12 |

| HEX0_D[3] | PIN_H13 |

| HEX0_D[4] | PIN_G12 |

| HEX0_D[5] | PIN_F12 |

| HEX0_D[6] | PIN_F13 |

| HEX0_DP   | PIN_D13 |

| HEX1_D[0] | PIN_A13 |

|-----------|---------|

| HEX1_D[1] | PIN_B13 |

| HEX1_D[2] | PIN_C13 |

| HEX1_D[3] | PIN_A14 |

| HEX1_D[4] | PIN_B14 |

| HEX1_D[5] | PIN_E14 |

| HEX1_D[6] | PIN_A15 |

| HEX1_DP   | PIN_B15 |

|           |                |           | 1       |

|-----------|----------------|-----------|---------|

| HEX2_D[0] | PIN_D15        | HEX3_D[0] | PIN_B18 |

| HEX2_D[1] | PIN_A16        | HEX3_D[1] | PIN_F15 |

| HEX2_D[2] | PIN_B16        | HEX3_D[2] | PIN_A19 |

| HEX2_D[3] | PIN_E15        | HEX3_D[3] | PIN_B19 |

| HEX2_D[4] | PIN_A17        | HEX3_D[4] | PIN_C19 |

| HEX2_D[5] | PIN_B17        | HEX3_D[5] | PIN_D19 |

| HEX2_D[6] | PIN_F14        | HEX3_D[6] | PIN_G15 |

| HEX2_DP   | PIN_A18 Rights | HEX3_DP   | PIN_G16 |

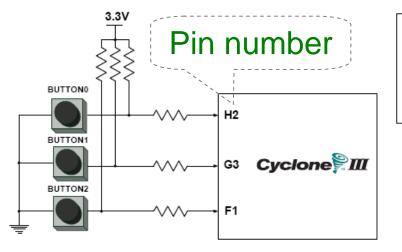

3 Pushbutton switches: Not pressed  $\rightarrow$  Logic High Pressed  $\rightarrow$  Logic Low

| Signal Name | FPGA Pin No. |

|-------------|--------------|

| BUTTON [0]  | PIN_H2       |

| BUTTON [1]  | PIN_G3       |

| BUTTON [2]  | PIN_F1       |

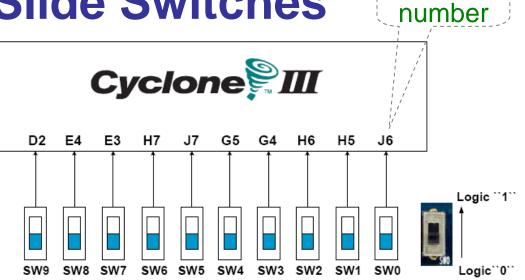

#### 10 Slide switches (Sliders): Up $\rightarrow$ Logic High Down $\rightarrow$ Logic

|       | -      |       |        |

|-------|--------|-------|--------|

| SW[0] | PIN_J6 | SW[5] | PIN_J7 |

| SW[1] | PIN_H5 | SW[6] | PIN_H7 |

| SW[2] | PIN_H6 | SW[7] | PIN_E3 |

| SW[3] | PIN_G4 | SW[8] | PIN_E4 |

| SW[4] | PIN_G5 | SW[9] | PIN_D2 |

Pin

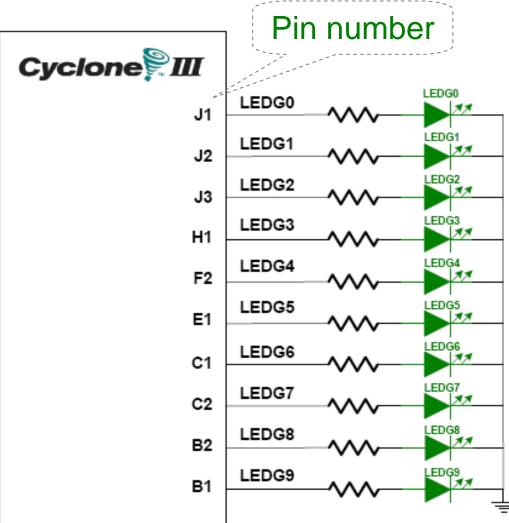

**LEDs**

#### 10 LEDs Opuput high $\rightarrow$ LED on Output low $\rightarrow$ LED off

| Signal Name | FPGA Pin No. |

|-------------|--------------|

| LEDG[0]     | PIN_J1       |

| LEDG[1]     | PIN_J2       |

| LEDG[2]     | PIN_J3       |

| LEDG[3]     | PIN_H1       |

| LEDG[4]     | PIN_F2       |

| LEDG[5]     | PIN_E1       |

| LEDG[6]     | PIN_C1       |

| LEDG[7]     | PIN_C2       |

| LEDG[8]     | PIN_B2       |

| LEDG[9]     | PIN_B1       |