## Class 14 Microprocessors

## Simplified Microcomputer System

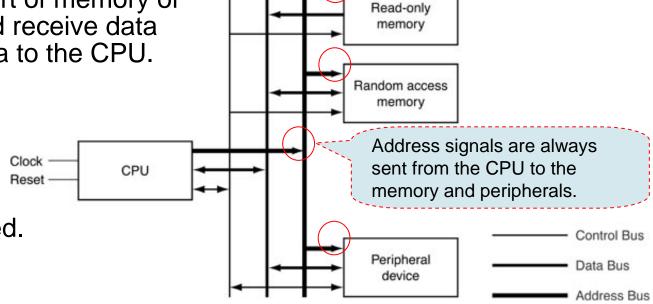

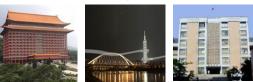

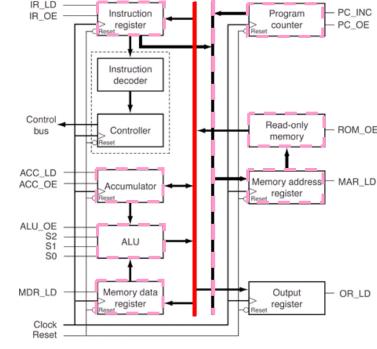

#### Control bus

- A set of control lines going from the CPU to various components.

- Direct the flow of data among modules of the microcomputer (MCU) by enabling and disabling the various data paths.

#### Address bus

- Specify which part of memory or peripheral should receive data from or send data to the CPU.

- Data bus

- Send or receive the actual data.

- Bus contention should be avoided.

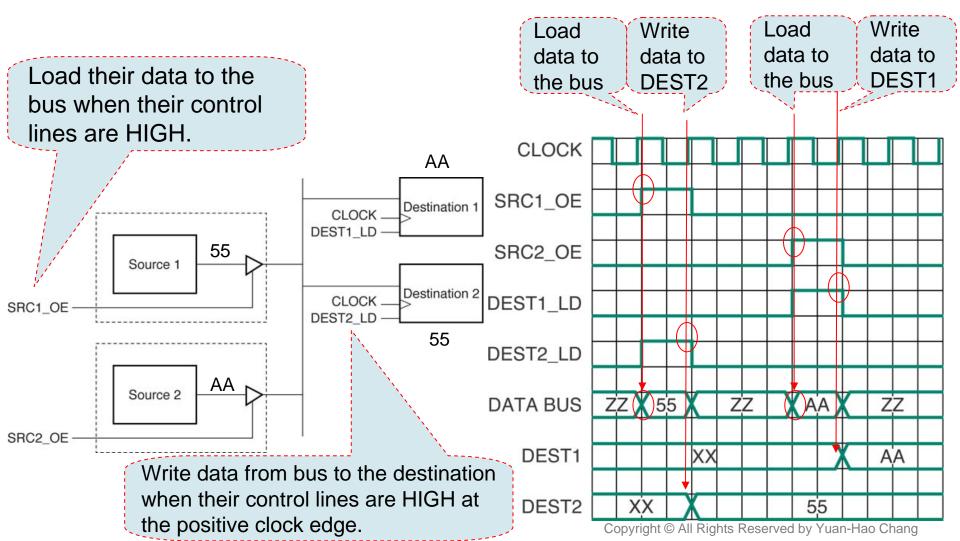

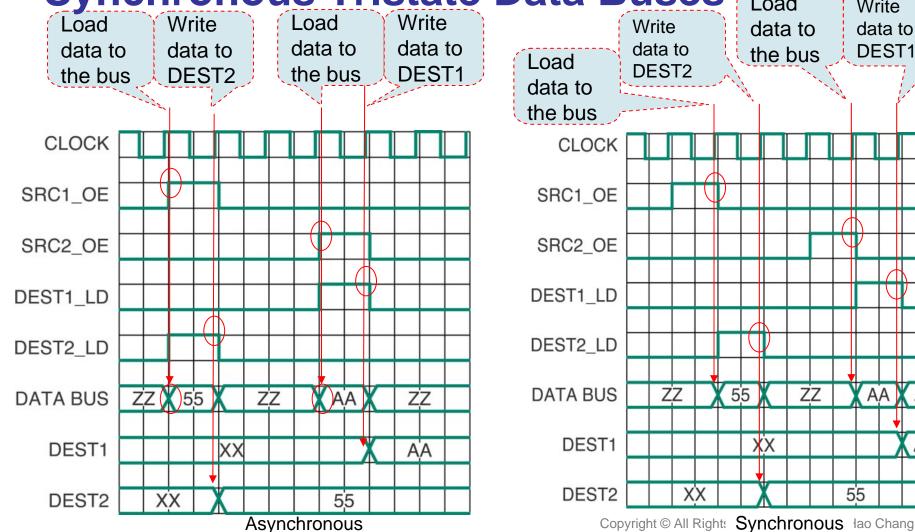

## **Asynchronous Tristate Data Bus**

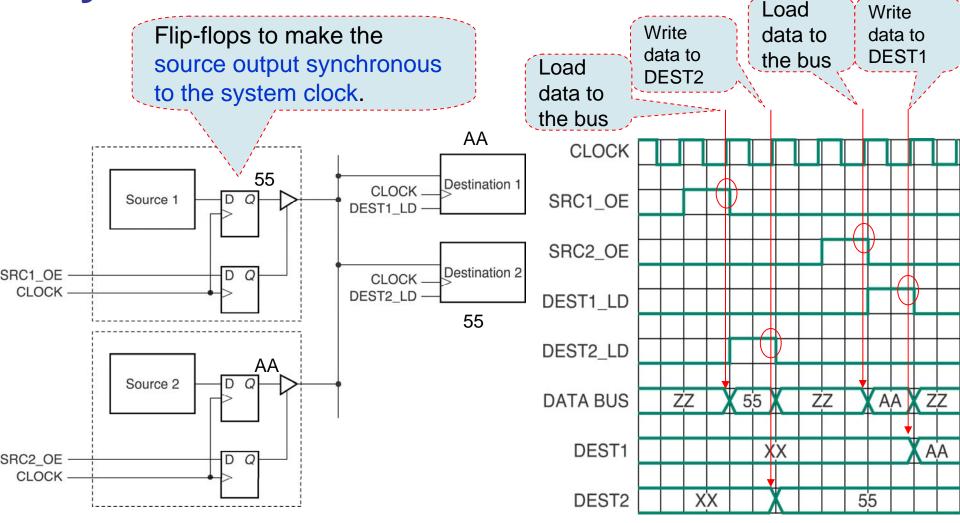

### Synchronous Tristate Data Bus

#### Comparison Between Asynchronous and Synchronous Tristate Data Buses Load Write

ŻΖ

AA

June 9, 2011

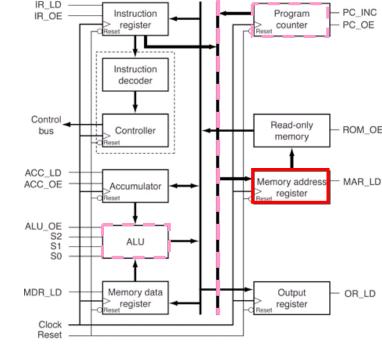

## **A Simple Microprocessor**

## A Simplified Op Codes and Program

#### Every instruction is fetched and then executed

| Instructions        | Op Codes     | Address                                               | Data     | Comment                     |  |

|---------------------|--------------|-------------------------------------------------------|----------|-----------------------------|--|

|                     | (Hex Values) | 0                                                     | 8C       | Load contents of C          |  |

| Add                 | 1            | 1                                                     | 1D       | Add contents of D           |  |

| Load                | 8            | 2                                                     | 90       | Send accumulator            |  |

| Output              | 9            |                                                       |          | contents to output register |  |

| Halt                | F            | 3                                                     | FO       | Halt                        |  |

| Simplified Op Codes |              | 4-B                                                   | Blank(00 | 00)                         |  |

|                     |              | С                                                     | 55       | Data for Load instruction   |  |

|                     |              | D                                                     | 64       | Data for Add instruction    |  |

|                     |              | A Simplified Program:                                 |          |                             |  |

|                     |              | Load, add, output, and halt (Stored in a 16-byte ROM) |          |                             |  |

|                     |              |                                                       |          |                             |  |

June 9, 2011

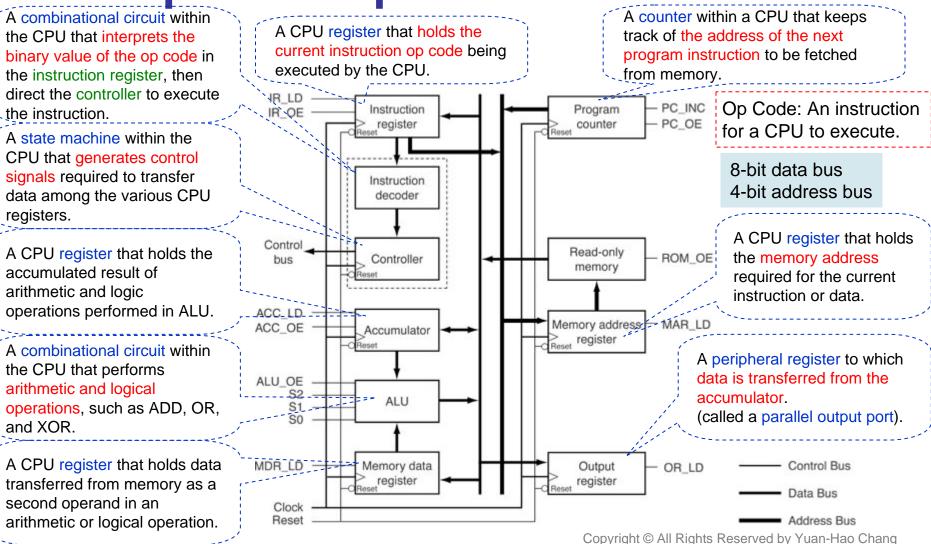

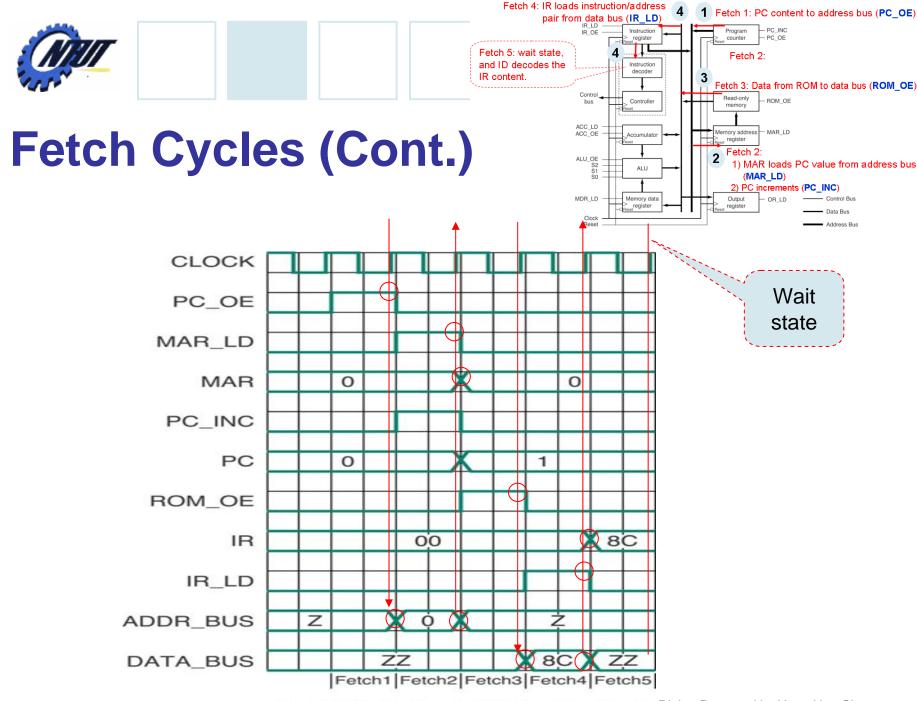

## **Fetch Cycles**

- Fetch 1:

- Transfer the contents of the **program counter (PC)** to the 4-bit address bus.

- Active control line: **pc\_oe**.

- Fetch 2:

- Transfer the PC address from the address bus to the memory address register (MAR).

- Increment the program counter so that it is ready to point to the next instruction.

- Active control line: mar\_ld, pc\_inc.

- Fetch 3:

- The value in MAR points to a ROM address containing an instruction to be executed. (4-bit op code and 4-bit operand address in this example)

- The data at the pointed ROM address is transferred to the 8-bit data bus.

- Active control line: rom\_oe.

- Fetch 4:

- The op code/address pair is transferred to the instruction register (IR) from the 8-bit data bus.

- Fetch 5:

- This is a "do nothing" state to wait for the data to stabilize.

- Instruction decoder (ID) decodes the IR contents and direct the CPU to begin executing the selected instruction.

Copyright © All Rights Reserved by Yuan-Hao Chang

June 9, 2011

### Fetch Cycles (Cont.)

Fetch Cycle (for LOAD instruction) Rights Reserved by Yuan-Hao Chang

| A ANTIT |

|---------|

|         |

| 1550    |

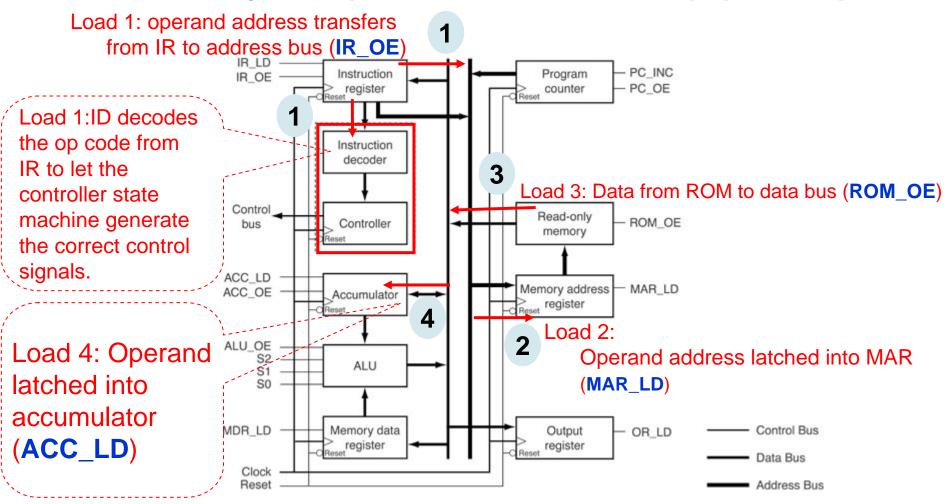

## **Execute Cycle (Load Instruction)**

- Load 1:

- The instruction/operand address pair in instruction register (IR) is split into the op code (4MSBs) and operand address (4LSBs).

- The op code goes by a direct connection to the instruction decoder (ID) in the controller state machine that determines the op code value and generate the correct control signals.

- The operand address is transferred to the address bus.

- Active control line: ir\_oe.

- Load 2:

- The MAR loads the contents of the address bus, thus latching the ROM address of the operand for the Load instruction.

- Active control line: mar\_ld.

- Load 3:

- Data transfers from the ROM to data bus.

- Active control line: rom\_oe.

- Load 4:

- Data transfers from the data bus to the accumulator.

- Active control line: **acc\_ld**.

#### **Execute Cycle (Load Instruction) (Cont.)**

Fetch Cycle (for LOAD instruction)

Execute Cycle (Load)

| <b>NNIT</b> |

|-------------|

| 4550        |

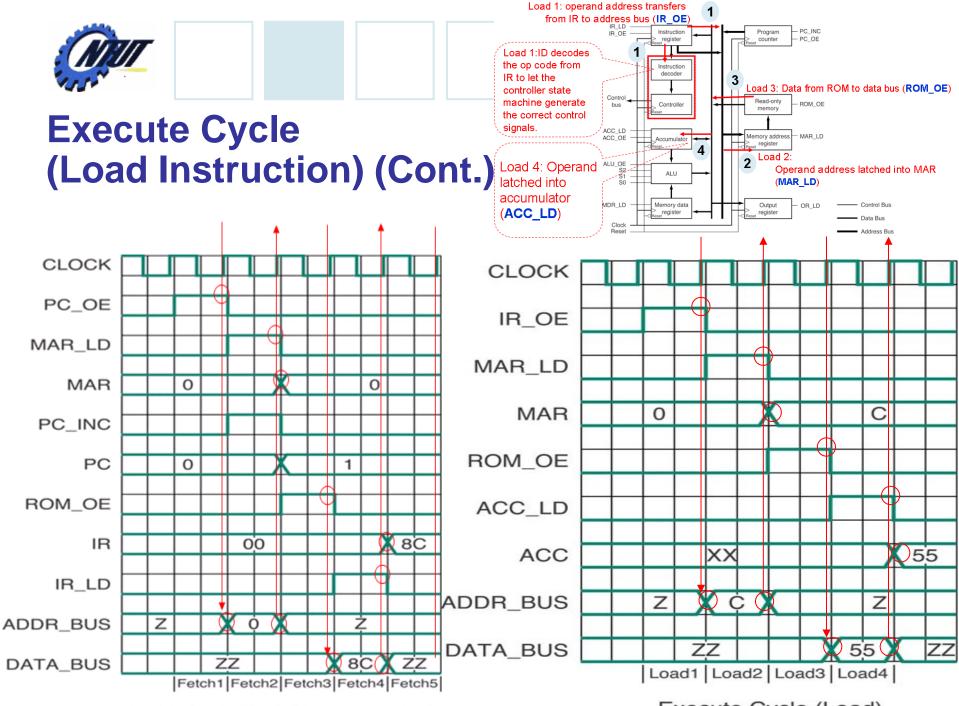

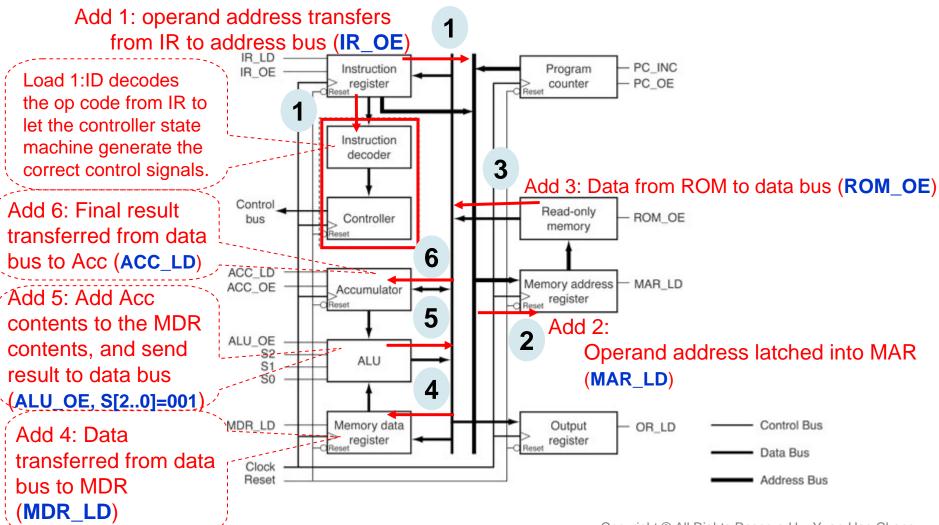

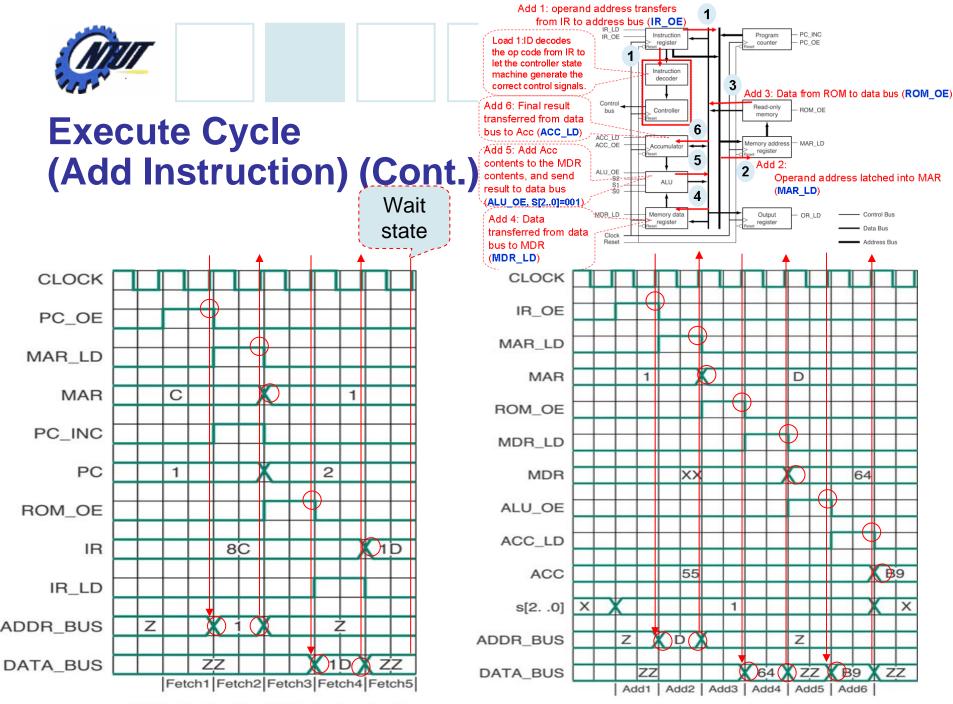

## Execute Cycle (Add Instruction)

- Add 1:

- The instruction/operand address pair in instruction register (IR) is split into the op code (4MSBs) and operand address (4LSBs).

- The op code goes by a direct connection to the instruction decoder (ID) in the controller state machine that \_ determines the op code value and generate the correct control signals.

- The operand address is transferred to the address bus.

- Active control line: ir oe, s[2..0]=001.

- Add 2:

- The MAR loads the contents of the address bus, thus latching the ROM address of the operand for the Load \_ instruction.

- Active control line: rom\_oe , s[2..0]=001.

- Add 3:

- Data transfers from the ROM to data bus.

- Active control line: rom\_oe , s[2..0]=001.

- Add 4:

- Transfer data from data bus to the **memory data register (MDR)**

- Active control line: acc oe, s[2..0]=001.

- Add 5:

- The ALU adds the accumulator contents to the MDR contents. \_

- The results transfers to the data bus.

- Active control line: alu\_oe, s[2..0]=001. —

- Add 6:

- The accumulator transfers the final result \_ on the data bus to accumulator..

- Active control line: acc Id, s[2..0]=001.

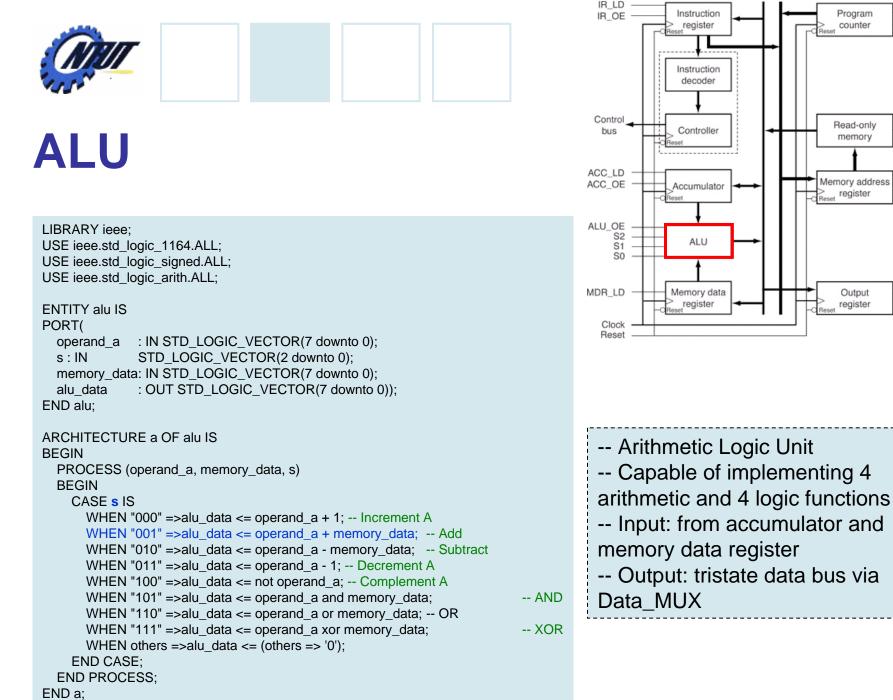

| S[20] | Function   | Operation   |  |

|-------|------------|-------------|--|

| 000   | Increment  | Acc + 1     |  |

| 001   | Add        | Acc + MDR   |  |

| 010   | Subtract   | Acc - MDR   |  |

| 011   | Decrement  | Acc - 1     |  |

| 100   | Complement | NOT Acc MDR |  |

| 101   | AND        | Acc AND     |  |

| 110   | OR         | Acc OR MDR  |  |

| 111   | XOR        | Acc XOR MDR |  |

|       |            |             |  |

#### ALU

#### **Execute Cycle (Add Instruction) (Cont.)**

Fetch Cycle (for ADD instruction)

Execute Cycle (Add)

Copyright © All Rights Reserved by Yuan-Hao Chang

PC\_INC

ROM OF

MAR\_LD

OR LD

PC OE

Program

counter

Read-only

memory

Memory address

register

Output

register

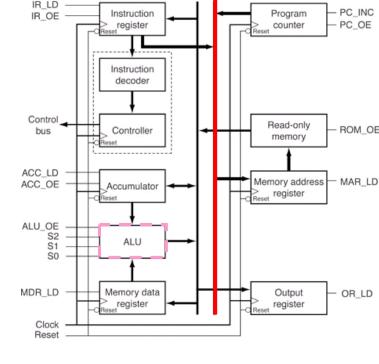

### **Address Bus**

LIBRARY ieee: USE ieee.std logic 1164.ALL; ENTITY address mux IS PORT( clock, reset, ir\_oe, pc\_oe : IN STD\_LOGIC; ir\_addr, pc\_addr : IN STD\_LOGIC\_VECTOR(3 downto 0); addr bus : OUT STD LOGIC VECTOR(3 downto 0)); END address mux; ARCHITECTURE mux OF address mux IS SIGNAL controls : STD\_LOGIC\_VECTOR(1 downto 0); BEGIN -- Concatenate output enable lines to use in -- selected signal assignment statement controls <= pc oe & ir oe; PROCESS(clock, reset) BEGIN IF(reset = '0')THEN addr\_bus <= (others = 'Z'); ELSIF(clock'EVENT and clock = '1')THEN CASE controls IS WHEN "01" => addr bus <= ir addr; WHEN "10" => addr\_bus <= pc\_addr; WHEN others = addr\_bus <= (others = 'Z'); END CASE: END IF; END PROCESS; END mux:

-- Address multiplexer with synchronous tristate outputs

-- Places instruction register or program counter contents

-- on address bus when selected.

Otherwise output is highimpedance.

| <b>NUT</b> |

|------------|

| 1551       |

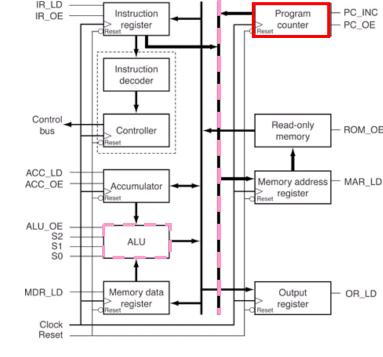

## **Program Counter**

```

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE ieee.std_logic_unsigned.ALL;

```

```

ENTITY program_counter IS

PORT(

clock, reset, pc_inc : IN STD_LOGIC;

pc_addr : BUFFER STD_LOGIC_VECTOR(3 downto 0));

END program_counter;

```

```

ARCHITECTURE pc OF program_counter IS

BEGIN

PROCESS(clock, reset)

BEGIN

IF(reset = '0')THEN

pc_addr <= (others => '0');

ELSIF(clock'EVENT and clock = '1')THEN

IF(pc_inc = '1')THEN

pc_addr <= pc_addr + 1;

END IF;

END IF;

END PROCESS;

END pc;

```

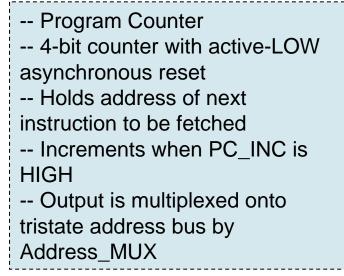

### **Memory Address Register**

```

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

```

```

ENTITY memory_address_register IS

PORT(

clock, reset, mar_ld : IN STD_LOGIC;

addr_bus : IN STD_LOGIC_VECTOR(3 downto 0);

rom_addr : OUT STD_LOGIC_VECTOR(3 downto 0));

END memory address register;

```

```

ARCHITECTURE mar OF memory_address_register IS

BEGIN

PROCESS(reset, clock)

BEGIN

IF(reset = '0')THEN

rom_addr <= (others => '0');

ELSIF(clock'EVENT and clock = '1')THEN

IF(mar_ld = '1')THEN

rom_addr <= addr_bus;

END IF;

END IF;

END PROCESS;

END mar;

```

| Time |

|------|

| NIUI |

| 1550 |

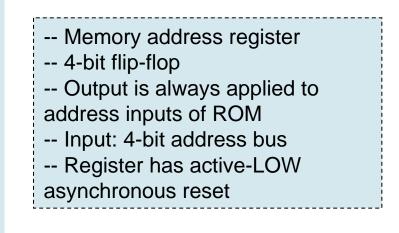

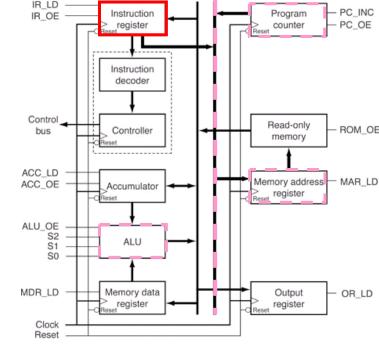

### **Instruction Register**

LIBRARY ieee; USE ieee.std\_logic\_1164.ALL; ENTITY instruction\_register IS

PORT(

data\_bus : IN STD\_LOGIC\_VECTOR(7 downto 0); clock, reset, ir\_ld : IN STD\_LOGIC; ir\_addr: OUT STD\_LOGIC\_VECTOR(3 downto 0); instruction: OUT STD\_LOGIC\_VECTOR(3 downto 0));

END instruction\_register;

ARCHITECTURE instr OF instruction\_register IS

-- Internal flip-flop values

```

SIGNAL q_int : STD_LOGIC_VECTOR(7 downto 0);

```

#### BEGIN

```

PROCESS(clock, reset)

```

#### BEGIN

IF (reset = '0') THEN

```

q_int <= (others => '0'); -- Clear all register bits

ELSIF (clock'EVENT and clock = '1') THEN

```

```

-- Load register on positive clock edge, if input is enabled

```

IF (ir\_ld = '1') THEN

```

q_int <= data_bus;

```

END IF;

END IF;

END PROCESS;

-- Split data into opcode and operand address instruction <= q\_int(7 downto 4);

```

ir_addr <= q_int(3 downto 0);

```

#### END instr;

-- Instruction register

-- 8-bit flip-flop with input and output enables

-- Input:op code (4-bit) and address of operand (4-bit) from system ROM

-- Output: opcode to Instruction Decoder module in controller, address to tristate address bus

-- Register has active-LOW asynchronous reset

|                                                                                                                                                                                          |                      |                                                                            | Instruction<br>register                                                                                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read Only Memory (RC                                                                                                                                                                     | )M)                  | ACC_LD                                                                     | Controller<br>et<br>ccumulator<br>et<br>ALU<br>ALU<br>Controller<br>Read-only<br>memory<br>Read-only<br>memory<br>Memory address<br>Reset register<br>Read-only<br>memory<br>Memory address |

| LIBRARY ieee;<br>USE ieee.std_logic_1164.ALL;<br>ENTITY rom16b IS<br>PORT(                                                                                                               |                      | Clock<br>Reset                                                             | emory data<br>register Output<br>ot Reset register OR_LD                                                                                                                                    |

|                                                                                                                                                                                          | Address              | Data<br>8C                                                                 | Comment<br>Load contents of C                                                                                                                                                               |

| rom_data : OUT STD_LOGIC_VECTOR(7 downto 0));<br>END rom16b;                                                                                                                             | 0                    | 80<br>1D                                                                   | Add contents of D                                                                                                                                                                           |

| END TOITTOD,                                                                                                                                                                             | 2                    | 90                                                                         | Send accumulator contents to                                                                                                                                                                |

|                                                                                                                                                                                          | ~                    | 50                                                                         |                                                                                                                                                                                             |

| ARCHITECTURE r OF rom16b IS                                                                                                                                                              |                      |                                                                            | output register                                                                                                                                                                             |

| BEGIN                                                                                                                                                                                    | 3                    | F0                                                                         | output register<br>Halt                                                                                                                                                                     |

| BEGIN<br>WITH rom_addr SELECT                                                                                                                                                            | 3<br>4-B             | F0<br>Blank(00)                                                            |                                                                                                                                                                                             |

| BEGIN<br>WITH rom_addr SELECT<br>rom_data <=                                                                                                                                             | -                    | -                                                                          |                                                                                                                                                                                             |

| BEGIN<br>WITH rom_addr SELECT<br>rom_data <=<br>x"8C" WHEN x"0",                                                                                                                         | 4-B                  | Blank(00)                                                                  | Halt                                                                                                                                                                                        |

| BEGIN<br>WITH rom_addr SELECT<br>rom_data <=<br>x"8C" WHEN x"0",<br>x"1D" WHEN x"1",                                                                                                     | 4-В<br>С             | Blank(00)<br>55                                                            | Halt Data for Load instruction                                                                                                                                                              |

| BEGIN<br>WITH rom_addr SELECT<br>rom_data <=<br>x"8C" WHEN x"0",<br>x"1D" WHEN x"1",<br>x"90" WHEN x"2",<br>x"F0" WHEN x"3",                                                             | 4-B<br>C<br>D        | Blank(00)<br>55<br>64<br>Blank(00)                                         | Halt<br>Data for Load instruction<br>Data for Add instruction                                                                                                                               |

| BEGIN<br>WITH rom_addr SELECT<br>rom_data <=<br>x"8C" WHEN x"0",<br>x"1D" WHEN x"1",<br>x"90" WHEN x"2",<br>x"F0" WHEN x"3",<br>x"55" WHEN x"C",                                         | 4-B<br>C<br>D<br>E-F | Blank(00)<br>55<br>64<br>Blank(00)<br>A Simpli                             | Halt<br>Data for Load instruction<br>Data for Add instruction<br>ified Program:                                                                                                             |

| BEGIN<br>WITH rom_addr SELECT<br>rom_data <=<br>x"8C" WHEN x"0",<br>x"1D" WHEN x"1",<br>x"90" WHEN x"2",<br>x"F0" WHEN x"2",<br>x"F0" WHEN x"3",<br>x"55" WHEN x"C",<br>x"64" WHEN x"D", | 4-B<br>C<br>D<br>E-F | Blank(00)<br>55<br>64<br>Blank(00)<br>A Simpli<br>Load, add,               | Halt<br>Data for Load instruction<br>Data for Add instruction<br>ified Program:<br>output, and halt                                                                                         |

| BEGIN<br>WITH rom_addr SELECT<br>rom_data <=<br>x"8C" WHEN x"0",<br>x"1D" WHEN x"1",<br>x"90" WHEN x"2",<br>x"F0" WHEN x"3",<br>x"55" WHEN x"C",                                         | 4-B<br>C<br>D<br>E-F | Blank(00)<br>55<br>64<br>Blank(00)<br>A Simpli<br>Load, add,<br>(Stored in | Halt<br>Data for Load instruction<br>Data for Add instruction<br>ified Program:                                                                                                             |

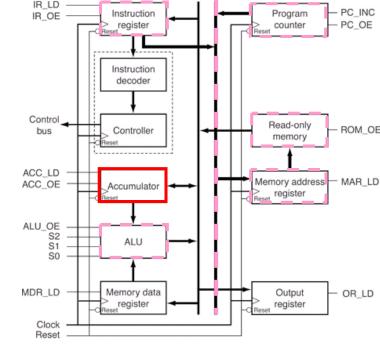

#### Accumulator

LIBRARY ieee; USE ieee.std\_logic\_1164.ALL;

```

ENTITY accumulator IS

PORT(

clock, reset, acc_Id : IN STD_LOGIC;

data_bus: IN STD_LOGIC_VECTOR(7 downto 0);

acc_data, operand_a : OUT STD_LOGIC_VECTOR(7 downto 0));

END accumulator;

```

#### ARCHITECTURE acc OF accumulator IS **BEGIN** PROCESS(clock, reset) BEGIN IF(reset = '0')THEN acc\_data <= (others => '0'); operand\_a <= (others = '0'); ELSIF(clock'EVENT and clock = '1')THEN IF(acc Id = '1')THENacc data <= data bus; operand\_a <= data\_bus; Data on Acc is END IF: directly applied to the END IF; ALU's operand. END PROCESS; END acc;

|   | Accumulator                                 |

|---|---------------------------------------------|

|   | 8-bit flip-flop with input and              |

|   | output enables                              |

|   | Input: 8-bit operand from data              |

| 1 | bus                                         |

|   | Output: 8-bit operand to aLU                |

|   | (direct connection) and 8-bit               |

| 1 | output to data bus                          |

|   | <ul> <li>Register has active-LOW</li> </ul> |

|   | asynchronous reset                          |

|   |                                             |

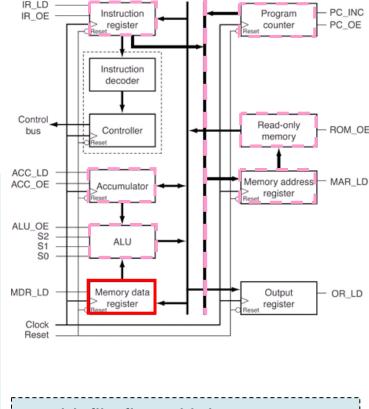

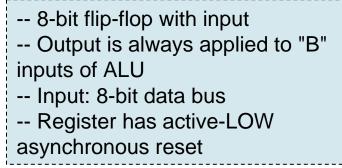

#### **Memory Data Register**

```

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

ENTITY memory_data_register IS

PORT(

data_bus : IN STD_LOGIC_VECTOR(7 downto 0);

clock, reset, mdr_ld : IN STD_LOGIC;

memory_data : OUT STD_LOGIC_VECTOR(7 downto 0));

END memory_data_register;

```

```

ARCHITECTURE mdr OF memory_data_register IS

BEGIN

PROCESS(clock, reset)

BEGIN

IF(reset = '0')THEN

-- Clear all register bits

memory_data <= (others => '0');

ELSIF (clock'EVENT and clock = '1') THEN

-- Load register on positive clock edge, if input is enabled

IF(mdr_ld = '1')THEN

memory_data <= data_bus;

END IF;

END IF;

END PROCESS;

END mdr ;

```

# **NHIT**

**Data Bus**

LIBRARY ieee; USE ieee.std\_logic\_1164.ALL;

ENTITY data\_mux IS

#### PORT(

clock, reset : IN STD\_LOGIC; rom\_data : IN STD\_LOGIC\_VECTOR(7 downto 0); -- ROM instruction/data acc\_data : IN STD\_LOGIC\_VECTOR(7 downto 0); -- Accumulator contents alu\_data : IN STD\_LOGIC\_VECTOR(7 downto 0); -- ALU contents rom\_oe, acc\_oe, alu\_oe : IN STD\_LOGIC; data bus : OUT STD\_LOGIC\_VECTOR(7 downto 0));

#### END data\_mux;

ARCHITECTURE a OF data\_mux IS

SIGNAL controls : STD\_LOGIC\_VECTOR(2 downto 0);

#### BEGIN

BEGIN

controls <= rom\_oe & acc\_oe & alu\_oe; PROCESS(clock, reset)

High impedance

High impedance

IF(reset = '0')THEN data\_bus <= (others => 'Z');

ELSIF(clock'EVENT and clock = '1')THEN CASE controls IS WHEN "100" =>data\_bus <= rom\_data; WHEN "010" =>data\_bus <= acc\_data; WHEN "001" =>data\_bus <= alu\_data; WHEN others =>data\_bus <= (others => 'Z'); END CASE:

END IF; END PROCESS:

END a;

-- Multiplexes data from ROM, Accumulator, or ALU onto tristate data bus

-- Each data input is separately enabled; only one enable permitted at a time.

| <b>NUT</b> |

|------------|

| 1550       |

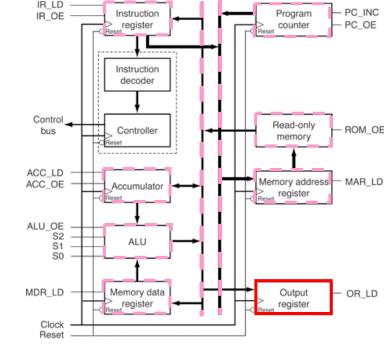

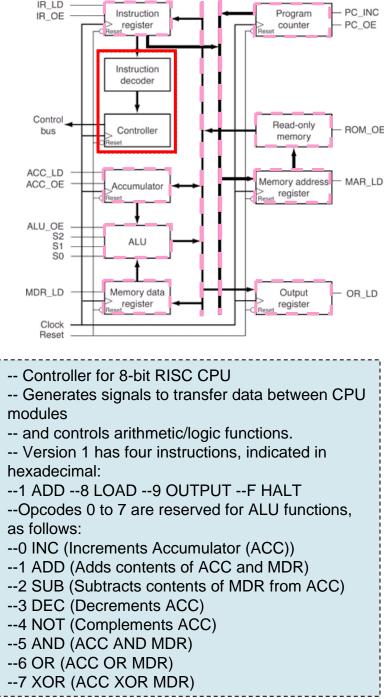

### **Output Register**

```

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

ENTITY output_register IS

PORT(

data_bus : IN STD_LOGIC_VECTOR(7 downto 0);

clock, reset, or_ld : IN STD_LOGIC;

output : OUT STD_LOGIC_VECTOR(7 downto 0));

END output_register;

```

```

ARCHITECTURE output OF output_register IS

BEGIN

PROCESS(clock, reset)

BEGIN

IF(reset = '0')THEN

-- Clear all register bits

output <= (others => '0');

ELSIF (clock'EVENT and clock = '1') THEN

-- Load register on positive clock edge, if input is enabled

IF(or_ld = '1')THEN

output <= data_bus;

END IF;

END IF;

END PROCESS;

END output ;

```

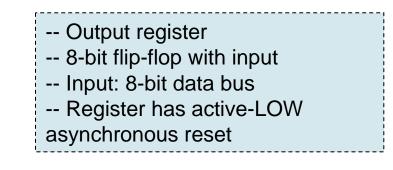

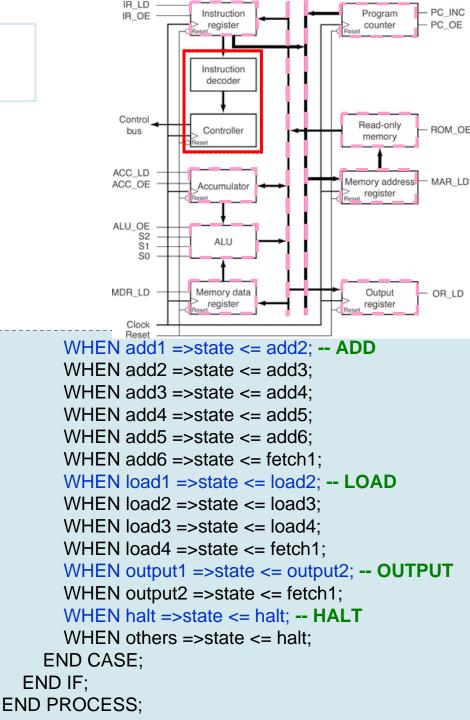

#### Controller

```

ENTITY controller_v1 IS

PORT(

clock, reset : IN

BIT:

instruction : IN

BIT_VECTOR(3 dowoto 0);

fetch, pc_inc, pc_oe : OUT

BIT:

ir Id, ir oe, mar Id, rom oe : OUT

BIT;

acc_ld, acc_oe, alu_oe, mdr_ld : OUT

BIT:

or_ld : OUT

BIT:

s:OUT

BIT VECTOR(2 downto 0));

END controller_v1;

ARCHITECTURE ctrl OF controller v1 IS

TYPE state type IS (

start, fetch1, fetch2, fetch3, fetch4, fetch5,

load1, load2, load3, load4,

add1, add2, add3, add4, add5, add6,

output1, output2, halt);

SIGNAL state : state_type;

SIGNAL control word : BIT VECTOR(15 downto 0);

BEGIN

PROCESS(clock, reset)

Initial state

BEGIN

IF(reset = '0')THEN

state <= start;

ELSIF(clock'EVENT and clock = '1')THEN

```

### **Controller (Cont.)**

-- Create state machine for instruction sequences. CASE state IS WHEN start =>state <= fetch1; -- Fetch cycle WHEN fetch1 =>state <= fetch2; WHEN fetch2 =>state <= fetch3; WHEN fetch3 =>state <= fetch4; WHEN fetch4 =>state <= fetch5; WHEN fetch5 => CASE instruction IS-- Decode instruction WHEN x"1" =>state <= add1; WHEN x"8" =>state <= load1; WHEN x"8" =>state <= load1; WHEN x"9" =>state <= output1; WHEN x"F" =>state <= halt; WHEN others =>state <= halt; END CASE;

June 9, 2011

29

### **Controller (Cont.)**

| Assign | control bus outputs. |

|--------|----------------------|

| fetch  | <=control_word(14);  |

| pc_inc | <=control_word(13);  |

| pc_oe  | <=control_word(12);  |

| ir_ld  | <=control_word(11); |

|--------|---------------------|

| ir_oe  | <=control_word(10); |

| mar_ld | <=control_word(9);  |

| rom_oe | <=control_word(8);  |

acc\_ld <=control\_word(7); acc\_oe <=control\_word(6); alu\_oe <=control\_word(5); mdr\_ld <=control\_word(4); or\_ld <=control\_word(3);</pre>

or\_ld <=control\_word(3); s <=control\_word(2 downto 0); -- Output decoder

- -- Assign output control lines for each control state

- -- "Fetch" output goes LOW to turn on LED during fetch cycle WITH state SELECT

control\_word <=

x"4000" WHEN start, -- Fetch LED OFF

x"1000" WHEN fetch1, -- pc\_oe x"2200" WHEN fetch2, -- pc\_inc, mar\_ld x"0100" WHEN fetch3, -- rom\_oe x"0800" WHEN fetch4, -- ir\_ld x"0000" WHEN fetch5, -- wait state

x"4400" WHEN load1, -- ir\_oe x"4200" WHEN load2, -- mar\_ld x"4100" WHEN load3, -- rom\_oe x"4080" WHEN load4, -- acc\_ld

x"4401" WHEN add1, -- ir\_oe, s=001 x"4201" WHEN add2, -- mar\_ld, s=001 x"4101" WHEN add3, -- rom\_oe, s=001 x"4011" WHEN add4, -- mdr\_ld, s=001 x"4021" WHEN add5, -- alu\_oe, s=001 x"4081" WHEN add6, -- acc\_ld, s=001

x"4040" WHEN output1, -- acc\_oe x"4008" WHEN output2, -- or\_ld

x"4000" WHEN others; -- Fetch LED stays OFF END ctrl;

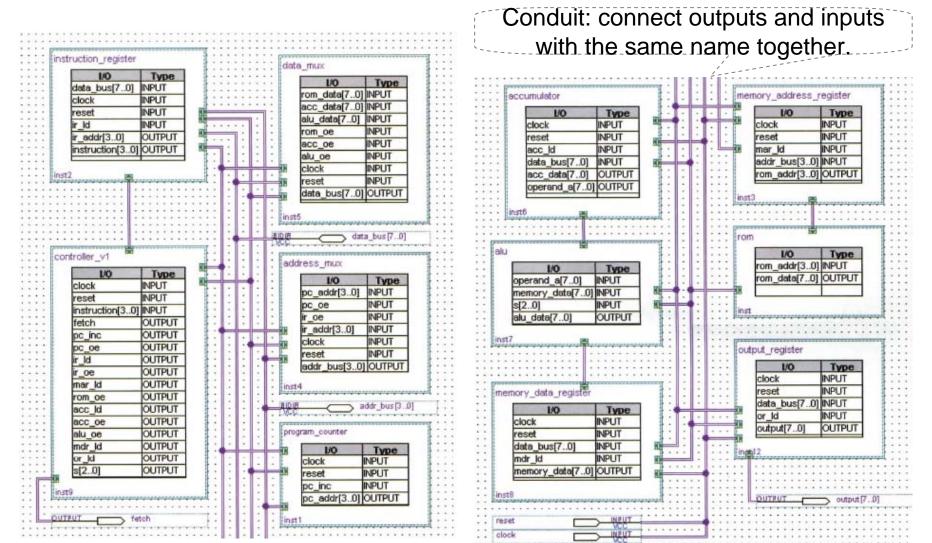

### Integration with Block Diagram File (.BDF)