## System Programming 系統程式

Yuan-Hao Chang (張原豪) johnsonchang@ntut.edu.tw Department of Electronic Engineering National Taipei University of Technology

October 8, 2010

## **Course Information**

#### • Lecturer:

- Yuan-Hao Chang

- Office: Room 207-2

- Phone: +886-2-2771-2171 ext. 2288

- Lecturing hours:

- 2:10 pm ~ 5:00 pm, Friday

- Classroom:

- Room 309, Third Education Building (三教 309)

- Textbook:

- System Software An Introduction to Systems Programming, 3rd Edition, 1997

- Author: Leland L. Beck Publisher: Addison Wesley (台北圖書代理), ISBN: 0-321-21177-4

- Course webpage:

- <u>http://www.ntut.edu.tw/~johnsonchang/courses/Algorithm201008/</u>

- Grading : (subject to changes)

- Homework: (30%), Midterm exam (30%), Final exam (30%), In-class performance (10%)

8, 2010

2

Copyright © All Rights Reserved by Yuan-Hao Chang

October 8, 2010

## **Outline of the Course**

- Background

- Assemblers

- Loaders and linkers

- Macro processors

- Compilers

- Operating systems

- Other system software

- Software engineering issues

3

## Chapter 1 Background

## Outline

- Introduction

- The Simplified Instructional Computer (SIC)

- CISC Machines

- RISC Machines

- References to Addressing Modes and Instruction Set

## Introduction

## **Objectives of This Course**

- This course is an introduction to the design and implementation of system software.

- System software consists of a variety of programs that support the operation of a computer.

- System software makes it possible for users to focus on an application or a problem to be solved, without knowing how the machine works internally.

- By understanding the system software, you will

- Gain a deeper understanding of how computers really work.

- Learn the relationship between system software and machine architecture.

| ÎNUT |

|------|

| 1550 |

## Examples of System Software

#### Assembler

Translate assembler-language programs into machine language, and may include *macro processor*.

#### • Loader or Linker

Load the resulting machine-language program into memory and prepared for execution.

#### Compiler

Translate programs in a high-level language (that are edited by text editor) into machine language.

#### Operating system

Control all of the processes running on the machine and take care of all the machine-level details.

#### Debugger

- Help detect errors in programs.

### **System Software and Machine Architecture**

- *Machine dependency* is the main difference between system software and application software.

- Application programs are concerned with the solution of some problem, using the computer as a tool.

- System programs are intended to support the operation and use of the computer itself. For example:

- Assemblers translate mnemonic instructions into machine code.

- **Compilers** generate machine language code, taking hardware characteristics into account.

- **Operating systems** are directly concerned with the management of nearly all of the resources of a computing system.

- There are some aspects of system software that do not directly depend upon the computing system. For example:

- The general design and logic of an assembler.

- Some code optimization techniques used by compilers.

## The Simplified Instructional Computer (SIC)

## Simplified Instructional Computer (SIC)

- It is difficult to distinguish whether the features of software are truly fundamental or solely depend on a particular machine.

- To avoid this problem, the fundamental functions of system software are discussed through a Simplified Instructional Computer (SIC).

- SIC is a hypothetical (假定的) computer that is carefully designed

- To include the hardware features most often found on real computers.

- To avoid unusual or irrelevant complexities.

- SIC provides the reader with a starting point to begin the design of system software for a new computer.

- SIC comes in two versions:

- The standard model: SIC

- The extra equipment version: SIC/XE

## SIC Machine Architecture

#### Memory

- -8 bits forms a byte.

- -3 consecutive bytes form a *word* (24 bits).

- All addresses on SIC are byte addresses.

- Words are addressed by the location of their lowest numbered byte.

- There are 32,768 (2<sup>15</sup>) bytes in the computer memory.

#### Registers

- Five registers, all of each have special uses.

- 24 bits long in each register.

| Mnemonic<br>(助記符號) | Number | Special use                                                                                            |

|--------------------|--------|--------------------------------------------------------------------------------------------------------|

| А                  | 0      | Accumulator; used for arithmetic operations                                                            |

| X                  | 1      | IndeX Register; used for (indexed) addressing                                                          |

| L                  | 2      | Linkage register; the Jump to Subroutine (JSUB) instruction stores the return address in this register |

| PC                 | 8      | <u>Program Counter</u> ; contains the address of the next instruction to be fetched for execution      |

| SW                 | 9      | <u>Status</u> <u>Word</u> ; contains a variety of information, including a Condition Code (CC)         |

October 8, 2010

## **SIC Machine Architecture (Cont.)**

#### Data formats

- Integers are stored as 24-bit binary numbers.

- Negative values are represented by 2's complement.

- Characters are stored using 8-bit ASCII codes.

- Floating-point hardware is not supported.

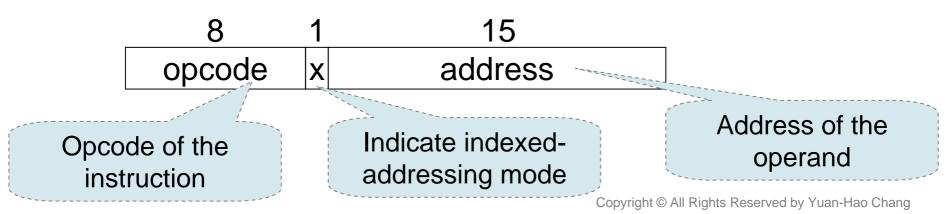

#### Instruction formats

#### Addressing Modes

- Indicated by the setting of the x bit in the instruction.

- The *target address* is calculated from the address given in the instruction.

- Target address of an instruction is *the address (of the operand)* that will be accessed by the instruction.

- Parentheses are used to indicate the contents of a register or a memory location.

$\cdot$  E.g., (X) represents the contents of register X.

| Mode    | Indication | Target address (TA) calculation |

|---------|------------|---------------------------------|

| Direct  | x = 0      | TA = address                    |

| Indexed | x = 1      | TA = address + (X)              |

#### Instruction Set

- Instructions that load and store registers

- E.g., LDA, LDX, STA, STX, etc.

- Integer arithmetic operations

- All arithmetic operations involve register A and a word in memory with the result left in register A.

- E.g., ADD, SUB, MUL, DIV

#### - Comparison instructions (COMP)

- COMP compares the value in register A with a word in memory, and sets a *condition code* (*CC*) to indicate the result (<, =, or >).

- Conditional jump instructions (JLT, JEQ, JGT)

- Test the setting of CC, and jump accordingly.

- Subroutine linkage

- JSUB jumps to the subroutine, placing the return address in register L.

- **RSUB** returns by jumping to the address contained in register L.

$\label{eq:copyright} \ensuremath{\mathbb{C}} \ensuremath{\mathsf{All}} \ensuremath{\mathsf{Rights}} \ensuremath{\mathsf{Reserved}} \ensuremath{\mathsf{by}} \ensuremath{\mathsf{Yuan-Hao}} \ensuremath{\mathsf{Chang}} \ensuremath{\mathsf{hab}} \ensuremath{\mathsf{Chang}} \ensuremath{\mathsf{hab}} \ensuremath{\mathsf{Chang}} \ensuremath{\mathsf{hab}} \ensure$

A complete list of instructions are listed in the appendix / references.

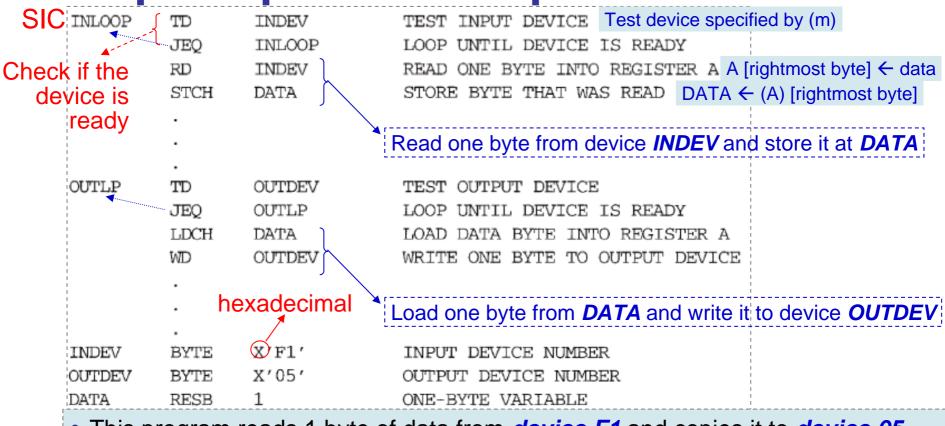

#### Input and Output

- Input and output are performed by transferring 1 byte at a time to or from the rightmost 8 bits of register A.

- Each device is assigned a unique 8-bit code.

- There are three I/O instructions, each of which specifies the *device* code as an operand:

- Test Device (TD) :

- · Test whether the addressed device is ready to send or received a byte of data.

- · The condition code is set to indicate the result of this test.

- » < means the device is ready.

- » = means the device is not ready.

- A program cannot transfer data until the device is ready.

- Read Data (RD): Read a byte from the device

- Write Data (WD): Write a byte to the device

## **SIC/XE Machine Architecture**

#### Memory

- The memory structure for SIC/XE is the same as SIC.

- The maximum memory available on a SIC/XE system is 1 megabytes (2<sup>20</sup> bytes).

- This increase leads to a change in *instruction formats* and *addressing modes*.

#### Registers

- Four additional registers (compared to SIC) are provided by SIC/XE:

| Mne-<br>monic | Number | Special use                                                 |

|---------------|--------|-------------------------------------------------------------|

| В             | 3      | Base register; used for (base-register relative) addressing |

| S             | 4      | General working register; no special use                    |

| Т             | 5      | General working register; no special use                    |

| F             | 6      | Floating-point accumulator (48 bits)                        |

#### Data formats

- SIC/XE provides the same data formats as the standard version.

- SIC/XE provides a 48-bit floating-point data type:

- The *fraction* (*f*) is interpreted as a value between 0 and 1.

- · The assumed binary point is immediately before the high-order bit.

- · For normalized floating-point, the high-order bit of the fraction must be 1.

- The *exponent* (*e*) is interpreted as an unsigned binary number between 0 and 2047.

- The sign of the float-point number is indicated by the value of s

- $\cdot$  0 = positive, 1 = negative.

- A value of zero is represented by setting all bits to 0.

| 1 | 11                                            | 36           |  |  |  |

|---|-----------------------------------------------|--------------|--|--|--|

| S | exponent ( <mark>e</mark> )                   | fraction (f) |  |  |  |

|   | The floating-point value = $f * 2^{(e-1024)}$ |              |  |  |  |

Copyright © All Rights Reserved by Yuan-Hao Chang

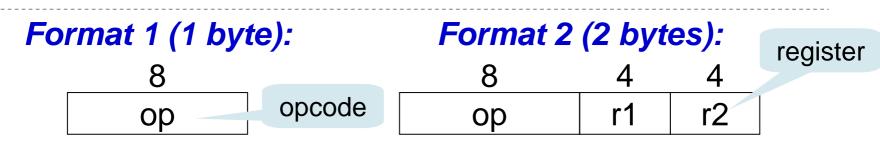

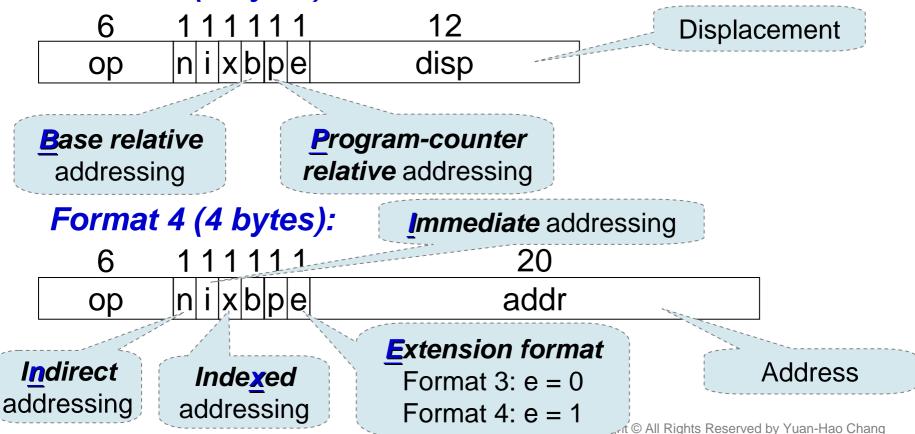

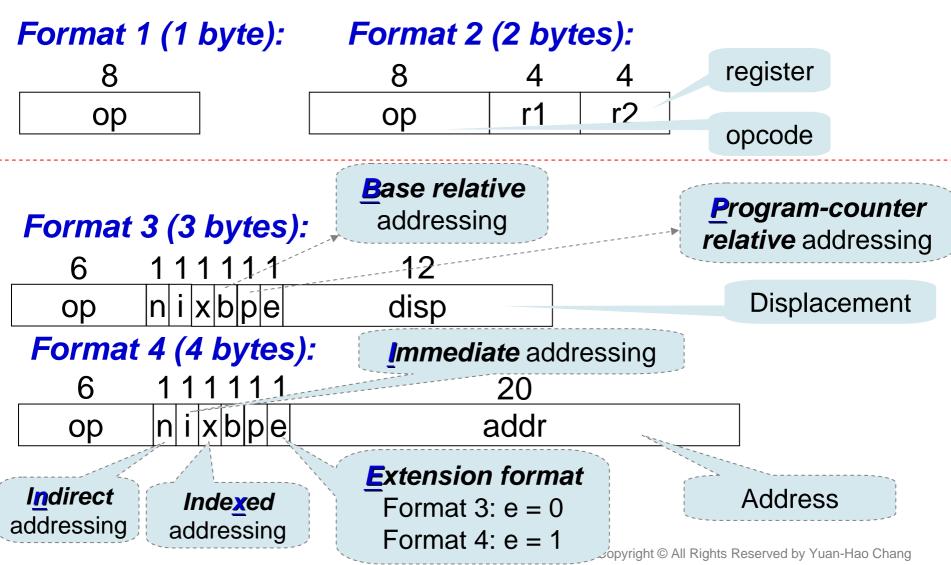

#### Instruction formats

- The 15-bit address field in SIC is no longer suitable due to the larger memory in SIC/XE.

- Two possible options:

- Use some form of *relative addressing* or

- Extend the address field to 20 bits.

- Four instructions formats:

- Formats 1 and 2 do not reference memory at all.

Copyright © All Rights Reserved by Yuan-Hao Chang

#### Instruction formats (Cont.)

#### Format 3 (3 bytes):

| ÎNUT |

|------|

| 1550 |

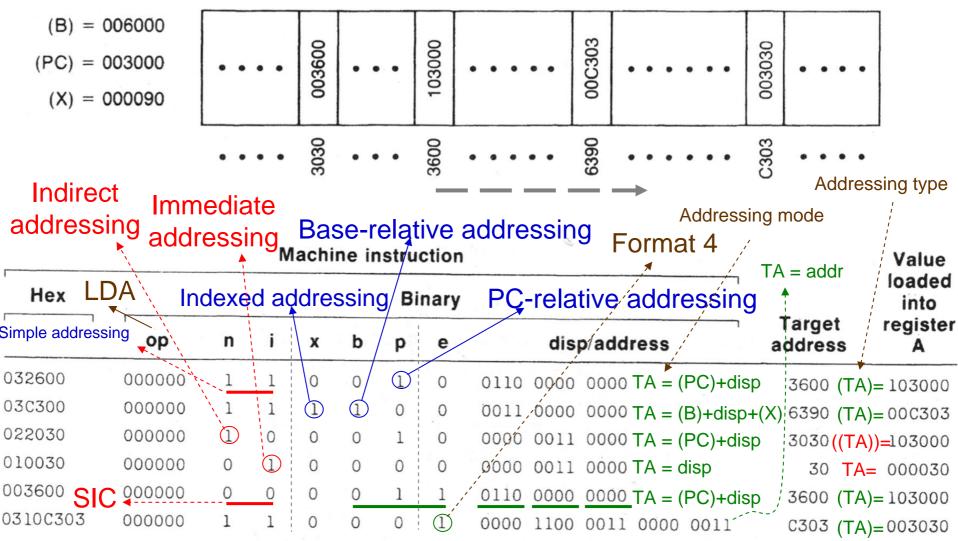

#### SIC/XE Machine Architecture (Cont.) • Addressing Modes – Target Address Calculation

(PC), (B), and (X) represent the contents of register PC, B, and X, respectively.

#### Format 3 (e=0)

| TA Calculation Mode | Indication            | Target address calculation Signed integer          |

|---------------------|-----------------------|----------------------------------------------------|

| Program-counter     | x=0, b=0, <b>p</b> =1 | $TA = (PC) + disp (-2048 \le disp \le 2047)$       |

| relative addressing | x=1, b=0, <i>p</i> =1 | $TA = (PC) + disp + (X) (-2048 \le disp \le 2047)$ |

| Base relative       | x=0, <b>b</b> =1, p=0 | $TA = (B) + disp (0 \le disp \le 4095)$            |

| addressing          | x=1, <i>b</i> =1, p=0 | $TA = (B) + disp + (X) (0 \le disp \le 4095)$      |

|                     | x=0, b=0, p=0         | TA = disp                                          |

| Direct addressing   | x=1, b=0, p=0         | TA = disp + (X) Unsigned integer                   |

- For a *Format 4 (e=1)* instruction, bits *b* and *p* are normally set to 0.

| TA Calculation Mode | Indication    | Target address calculation |

|---------------------|---------------|----------------------------|

| Direct addressing   | x=0, b=0, p=0 | TA = addr                  |

| Direct addressing   | x=1, b=0, p=0 | TA = addr + (X)            |

- Addressing Types How The Target Address Is Used

- Simple addressing: The target address is taken as the address of the operand value.

- Immediate addressing: The target address is used as the operand value.

- Indirect addressing: The value of the word at the location given by the target address is the address of the operand value.

| TA Addressing Type   | Indication            | Operand value                                                                                       |

|----------------------|-----------------------|-----------------------------------------------------------------------------------------------------|

|                      | n=0, i=0              | (TA) $\rightarrow$ for SIC machine, because the 8-bit binary opcodes of SIC instructions end in 00. |

| Simple addressing    |                       | b/p/e/disp = 15-bit <u>address</u> field of SIC instruction                                         |

|                      | n=1, i=1              | (TA) $\rightarrow$ for SIC/XE machine                                                               |

| Immediate addressing | n=0, <i>i</i> =1, x=0 | ТА                                                                                                  |

| Indirect addressing  | <i>n</i> =1, i=0, x=0 | ((TA))                                                                                              |

Indexed addressing cannot be used with immediate or indirect addressing modes. (x=0)

- Addressing modes for Format 3 and Format 4 instructions.

- Combinations of addressing bits not in this table are errors.

- Assembler language notation:

- c indicates a constant between 0 and 4095.

- *m* indicates a *memory address* or a *constant value* larger than 4095.

- + indicates extended format (i.e., Format 4)

- @ indicates a indirect addressing

- # indicates an *immediate addressing*

- X indicates register X (using indexed addressing)

- Letters in Notes

- 4 Format 4 instruction

- D Direct-addressing instruction

- A Program-counter relative or base relative mode

- S Compatible with standard SIC instructions. Operand value can be between 0 and 32,767.

| be                | mode                        | sion                              |                                        |         |       |

|-------------------|-----------------------------|-----------------------------------|----------------------------------------|---------|-------|

| Addressir<br>type | ng Flag bits<br>n i x b p e | Assembler<br>language<br>notation | Calculation<br>of target<br>address TA | Operand | Notes |

| Simple            | 110000                      | op c                              | disp                                   | (TA)    | D     |

|                   | 110001                      | +op m                             | addr                                   | (TA)    | 4 D   |

|                   | 110010                      | op m                              | (PC) + disp                            | (TA)    | А     |

|                   | 110100                      | op m                              | (B) + disp                             | (TA)    | А     |

|                   | 111000                      | op c,X                            | disp + (X)                             | (TA)    | D     |

|                   | 111001                      | +op m,X                           | addr + (X)                             | (TA)    | 4 D   |

|                   | 111010                      | op m,X                            | (PC) + disp + (X)                      | (TA)    | А     |

|                   | 111100                      | op m,X                            | $(B) + \mathrm{disp} + (X)$            | (TA)    | А     |

| with SIC          | ole                         | op m                              | b/p/e/disp                             | (TA)    | DS    |

| instructio        |                             | op m,X                            | b/p/e/disp + (X)                       | (TA)    | D S   |

| Indirect          | 100000                      | op @c                             | disp                                   | ((TA))  | D     |

|                   | $1 \ 0 \ 0 \ 0 \ 1$         | +op @m                            | addr                                   | ((TA))  | 4 D   |

|                   | 100010                      | op @m                             | (PC) + disp                            | ((TA))  | А     |

|                   | 100100                      | op @m                             | (B) + disp                             | ((TA))  | А     |

| Immediate         | 010000                      | op #c                             | disp                                   | TA      | D     |

|                   | 010001                      | +op #m                            | addr                                   | TA      | 4 D   |

|                   | 010010                      | op #m                             | (PC) + disp                            | TA      | А     |

|                   |                             |                                   |                                        |         |       |

Addressing Exten

010100

op #m

(B) + disp

TA

Α

Addressing

typ

#### Instruction Set

- SIC/XE provides all of the instructions that are available on SIC.

- Some extended instructions are supported.

- Load and store new registers

- · E.g., *LDB*, *STB*, etc.

- Floating-point arithmetic operations

- · E.g., ADDF, SUBF, MULF, DIVF

- Register-to-register arithmetic operations

- · E.g., RMO (register move operation), ADDR, SUBR, MULR, DIVR

- Special supervisor call instruction (SVC)

- This instruction generates an interrupt that can be used for communication with the operating system.

26

#### Input and Output

- The I/O instructions supported by SIC are also available on SIC/XE.

- I/O channels that can be used to perform input and output while the CPU is executing other instructions.

- This allows overlap of computing and I/O.

- **SIO**, **TIO**, and **HIO** are used to *start*, *test*, and *halt* the operation of I/O channels.

### **Expression Convention**

- Parentheses are used to denote the contents of a register or memory location.

- $-A \leftarrow (m..m+2)$  specifies that the contents of the memory locations *m* through m+2 are loaded into register *A*.

- m..m+2 (A) specifies that the contents of register A are stored in the word that begins at address m.

- -(A): (m..m+2) specifies that the contents of register A and memory location m through m+2 are compared.

#### **Sample Data Movement** LOAD CONSTANT 5 INTO REGISTER A $A \leftarrow (FIVE)$ SIC FIVE LDA ALPHA $\leftarrow$ (A) STA ALPHA STORE IN ALPHA LOAD CHARACTER 'Z' INTO REGISTER A A $\leftarrow$ (CHARZ) LDCH CHARZ Load a word STCH C1 STORE IN CHARACTER VARIABLE C1 $C1 \leftarrow (A)$ Reserve one word of storage/variable for use by the program Load a character ONE-WORD VARIABLE ALPHA RESW Reserve one byte of FIVE WORD 5 ONE-WORD CONSTANT storage/*constant* C'Z' CHARZ BYTE ONE-BYTE CONSTANT initialized to 'Z' ONE-BYTE VARIABLE C1 RESB Reserve one byte of storage/variable for use by the program #5 LOAD VALUE 5 INTO REGISTER A $A \leftarrow 5$ LDA SIC/XE STORE IN ALPHA $\leftarrow$ (A) ALPHA STA LOAD ASCII CODE FOR 'Z' INTO REG A $A \leftarrow 90$ LDA #90 STCH C1STORE IN CHARACTER VARIABLE C1 $C1 \leftarrow (A)$ Immediate addressing Reserve one word of storage/variable for use by the program AL PHA RESW ONE-WORD VARIABLE C1ONE-BYTE VARIABLE RESB 1 Hao Chang

## Sample Arithmetic Operations

|                          |                                                | IA = (ALP)                                           | $\Pi A) + (\Pi V C R) -$                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------|------------------------------------------------|------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| comr                     | SIC                                            | LDA<br>ADD<br>SUB<br>STA<br>LDA<br>ADD<br>SUB<br>STA | ALPHA<br>INCR<br>ONE<br>BETA<br>GAMMA<br>INCR<br>ONE<br>DELTA | LOAD ALPHA INTO REGISTER A $A \leftarrow (ALPHA)$<br>ADD THE VALUE OF INCR $A \leftarrow (A) + (INCR)$<br>SUBTRACT 1 $A \leftarrow (A) - (ONE)$<br>STORE IN BETA BETA $\leftarrow (A)$<br>LOAD GAMMA INTO REGISTER A $A \leftarrow (GAMMA)$<br>ADD THE VALUE OF INCR $A \leftarrow (A) + (INCR)$<br>SUBTRACT 1 $A \leftarrow (A) - (ONE)$<br>STORE IN DELTA DELTA $\leftarrow (A)$<br>$\rightarrow$ DELTA = (GAMMA) + (INCR) - 1 |

| constant -<br>variable < | ONE<br>ALPHA<br>BETA<br>GAMMA<br>DELTA<br>INCR | WORD<br>RESW<br>RESW<br>RESW<br>RESW<br>RESW         |                                                               | ONE-WORD CONSTANT<br>ONE-WORD VARIABLES<br>Ogram is to store the value (ALPHA +<br>1) in BETA, and the value (GAMMA<br>-1) in DELTA.                                                                                                                                                                                                                                                                                             |

## **Sample Arithmetic Operations (Cont.)**

|           | LDS      | INCR      | TOAD VALUE OF THE THE AND DECTEMEN $C < (INCD)$          |

|-----------|----------|-----------|----------------------------------------------------------|

| SIC/XE    |          |           | LOAD VALUE OF INCR INTO REGISTER S S $\leftarrow$ (INCR) |

| 1         | LDA      | ALPHA     | LOAD ALPHA INTO REGISTER A $\land \leftarrow$ (ALPHA)    |

| 1         | ADDR     | S,A       | ADD THE VALUE OF INCR $A \leftarrow (A) + (S)$           |

| <br> <br> | SUB      | #1        | SUBTRACT 1 A $\leftarrow$ (A) - 1                        |

|           | STA      | BETA      | STORE IN BETA $\leftarrow$ (A)                           |

|           | LDA      | GAMMA     | LOAD GAMMA INTO REGISTER A A $\leftarrow$ (GAMMA)        |

|           | ADDR     | S,A       | ADD THE VALUE OF INCR $A \leftarrow (A) + (S)$           |

|           | SUB      | #1        | SUBTRACT 1 A $\leftarrow$ (A) - 1                        |

|           | STA      | DELTA     | STORE IN DELTA $\rightarrow$ (A)                         |

|           |          |           |                                                          |

|           |          |           |                                                          |

|           |          |           |                                                          |

| -         |          |           | ONE WORD VARIABLES                                       |

| ALPHA     | RESW     | 1         |                                                          |

| BETA      | RESW     |           | avoids having to fetch INCR from memory                  |

| GAMMA     | RESW     | 1 each    | time it is used in a calculation.                        |

| DELTA     | RESW     | 1 Imm     | adiata addrassing is used for the constant               |

| INCR      | RESW     |           | ediate addressing is used for the constant               |

| TIACL     | 1/12/0/4 | + I I I I | he subtraction operations.                               |

# SIC Indexed addressing

| MOVECH    | LDX<br>LDCH<br>STCH<br>TIX<br>JLT | STR1 X<br>STR2,X<br>ELEVEN | INITIALIZE INDEX REGISTER TO 0 $X \leftarrow (ZERO)$<br>LOAD CHARACTER FROM STR1 INTO REG A $A \leftarrow (STR1 + (X)$<br>STORE CHARACTER INTO STR2 $STR2 + (X) \leftarrow (A)$<br>ADD 1 TO INDEX, COMPARE RESULT TO 11 $X \leftarrow (X) + 1$<br>LOOP IF INDEX IS LESS THAN 11 (X): (ELEVEN)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|-----------|-----------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1         |                                   |                            | PC ← MOVECH if CC set to <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|           |                                   |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| <br> <br> |                                   |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| STR1      | BYTE                              | C'TEST STRING              | G' 11-BYTE STRING CONSTANT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| STR2      | RESB                              | 11                         | 11-BYTE VARIABLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|           |                                   |                            | ONE-WORD CONSTANTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| ZERO      | WORD                              | 0                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| ELEVEN    | WORD                              | • The loo                  | p copies one 11-byte character string to another.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| <br> <br> |                                   | • The ind                  | ex register X is initialized to zero.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|           |                                   | • <i>TIX</i> per           | forms two functions:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|           |                                   | •                          | t it adds 1 to the value in register X.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|           |                                   | – The                      | The still as a second data as a second state of the state of the second state of the s |  |  |

SIC/XF

#### Sample Looping and Indexing (Cont.) Immediate addressing

|        | LDT  | ( <b>∲</b> 11 | INITIALIZE REGISTER T TO 11 T $\leftarrow$ 1 | 1                    |

|--------|------|---------------|----------------------------------------------|----------------------|

|        | LDX  | #0            | INITIALIZE INDEX REGISTER TO 0               | X ← 0                |

| MOVECH | LDCH | STR1,X        | LOAD CHARACTER FROM STR1 INTO REG            | 3 A                  |

|        | STCH | STR2,X        | STORE CHARACTER INTO STR2                    |                      |

|        | TIXR | т             | ADD 1 TO INDEX, COMPARE RESULT TO            | ) 11                 |

|        | JLT  | MOVECH        | LOOP IF INDEX IS LESS THAN 11                |                      |

|        |      |               |                                              | $X \leftarrow (X) +$ |

|        |      |               |                                              | (X) : (T)            |

|        |      |               |                                              |                      |

| STR1   | BYTE | C'TEST STR    | ING' 11-BYTE STRING CONSTANT                 |                      |

| STR2   | RESB | 11            | 11-BYTE VARIABLE                             |                      |

|        |      |               |                                              |                      |

- **TIXR** allows to compare index register **X** with another register. - This is efficient because the value does not have to be fetched

- from memory each time the loop is executed.

Copyright © All Rights Reserved by Yuan-Hao Chang

## **Another Sample Indexing and Looping**

|           | SIC       | LDA  | ZERO                | INITIALIZE INDEX VALU                 |                                                                                    |  |

|-----------|-----------|------|---------------------|---------------------------------------|------------------------------------------------------------------------------------|--|

|           |           | STA  | INDEX               | INDEX $\leftarrow$ (A); // initialize |                                                                                    |  |

|           | ADDLP     | LDX  | INDEX               | LOAD INDEX VALUE INTO                 |                                                                                    |  |

| (         | Gamma ← ∫ | LDA  | ALPHA,X             | LOAD WORD FROM ALPHA                  | INTO REGISTER A $\leftarrow$ (ALPHA + (X))                                         |  |

|           | (ALPHA)   | ADD  | BETA, X             | ADD WORD FROM BETA A                  | $\leftarrow$ (A) + (BETA+(X))                                                      |  |

|           | + (BETA)  | STA  | GAMMA, X            | STORE THE RESULT IN A                 | $O_{\Lambda}(M)$                                                                   |  |

|           | Move to   | LDA  | INDEX               | ADD 3 TO INDEX VALUE                  |                                                                                    |  |

|           | next word | ADD  | THREE               | $A \leftarrow (A) + (THREE); // inc$  | prease 3                                                                           |  |

|           |           | STA  | INDEX               | INDEX $\leftarrow$ (A);               |                                                                                    |  |

|           |           | COMP | K300                | COMPARE NEW INDEX VAL                 | JUE TO 300 (A): (K300)                                                             |  |

| - <u></u> |           | JLT  | ADDLP               | LOOP IF INDEX IS LESS                 | G THAN 300 PC ← ADDLP if CC set to <                                               |  |

| 1         |           |      |                     |                                       |                                                                                    |  |

|           |           |      |                     |                                       | Imbersome because register A must be<br>A and BETA, and <i>incrementing</i> INDEX. |  |

|           | INDEX     | RESW | 1                   | ONE-WORD VARIABLE FOR                 | R INDEX VALUE                                                                      |  |

|           |           |      |                     | ARRAY VARIABLES100                    | WORDS EACH                                                                         |  |

|           | ALPHA     | RESW | 100                 |                                       | <ul> <li>This loop adds elements of ALPHA</li> </ul>                               |  |

| i<br>i    | BETA      | RESW | 100 <b>≻100-</b> v  | vord arrays/variables                 | and BETA, and stores the results in                                                |  |

| 1         | GAMMA     | RESW | 100                 |                                       | the elements of GAMMA.                                                             |  |

|           |           |      |                     | ONE-WORD CONSTANTS                    |                                                                                    |  |

|           | ZERO      | WORD | 0                   |                                       | <ul> <li>TIX instruction always adds 1 to</li> </ul>                               |  |

| i<br>i    | K300      | WORD | 300 <b>≻ ONE-</b> \ | word constants                        | register <b>X</b> , so it is not suitable to                                       |  |

|           | THREE     | WORD | 3                   |                                       | this program.                                                                      |  |

# Another Sample Indexing and Looping (Cont.)

| SIC/XE    | LDS<br>LDT | #3<br>#300 | INITIALIZE REGISTER S TO 3 $S \leftarrow 3$<br>INITIALIZE REGISTER T TO 300 $T \leftarrow 300$                                         |  |

|-----------|------------|------------|----------------------------------------------------------------------------------------------------------------------------------------|--|

|           | LDX        | #0         | INITIALIZE INDEX REGISTER TO $0 \times \leftarrow 0$                                                                                   |  |

| ADDLP     | LDA        | ALPHA,     |                                                                                                                                        |  |

| GAMMA ← J | ADD        | BETA, X    |                                                                                                                                        |  |

| (ALPHA)   | STA        | GAMMA,     |                                                                                                                                        |  |

| + (BETA)  |            |            |                                                                                                                                        |  |

|           | ADDR       | S,X        | ADD 3 TO INDEX VALUE $X \leftarrow (X) + (S)$ ; // move to next word                                                                   |  |

|           | COMPR      | Х,Т        | COMPARE NEW INDEX VALUE TO 300 $(\times)$ : (T)                                                                                        |  |

|           | JLT        | ADDLP      | LOOP IF INDEX VALUE IS LESS THAN 300                                                                                                   |  |

|           | •          |            |                                                                                                                                        |  |

|           |            |            |                                                                                                                                        |  |

|           |            |            |                                                                                                                                        |  |

|           |            |            | ARRAY VARIABLES100 WORDS EACH                                                                                                          |  |

| ALPHA     | RESW       | 100        |                                                                                                                                        |  |

| BETA      | RESW       | 100        | <ul> <li>Register S: Store 3 for the one-word increment.</li> <li>Register T: Store 300 for the number of words in an array</li> </ul> |  |

| GAMMA     | RESW       | 100        |                                                                                                                                        |  |

|           |            |            | Register <b>X</b> : Indicate the <b>offset (index value)</b> to the starting of an array.                                              |  |

## **Simple Input and Output**

- This program reads 1 byte of data from *device F1* and copies it to *device 05*.

- **TD** instruction is to test whether the device is ready.

- If the device is *ready* to transmit data, the condition code is set to "*less than*."

- If the device is not ready, the condition is set to "equal."

37

### **Sample Subroutine Call**

| SIC             | JSUB                                                 | READ                                                                                                                                                                                                                                                                             | CALL READ SUBROUTINE $L \leftarrow (PC)$ ; PC $\leftarrow$ READ                                                                                                                                                                                                                                        |                              |

|-----------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

|                 |                                                      |                                                                                                                                                                                                                                                                                  | Before value of PC is stored in L, PC is advanced by 3 (pointin to the next instruction)                                                                                                                                                                                                               | ng                           |

| READ<br>RLOOP   | LDX<br>TD<br>JEQ<br>RD<br>STCH<br>TIX<br>JLT<br>RSUB | ZERO<br>INDEV<br>RLOOP<br>INDEV<br>RECORD,X<br>K100<br>RLOOP                                                                                                                                                                                                                     | SUBROUTINE TO READ 100-BYTE RECORD<br>INITIALIZE INDEX REGISTER TO 0<br>TEST INPUT DEVICE<br>LOOP IF DEVICE IS BUSY<br>READ ONE BYTE INTO REGISTER A<br>STORE DATA BYTE INTO RECORD<br>ADD 1 TO INDEX AND COMPARE TO 100<br>LOOP IF INDEX IS LESS THAN 100<br>EXIT FROM SUBROUTINE $PC \leftarrow (L)$ | 1 and<br>a 100-<br>a<br>DRD. |

| INDEV<br>RECORD | BYTE<br>RESB                                         | X'F1'<br>100                                                                                                                                                                                                                                                                     | INPUT DEVICE NUMBER<br>100-BYTE BUFFER FOR INPUT RECORD                                                                                                                                                                                                                                                |                              |

| ZERO<br>K100    | WORD<br>WORD                                         | <ul> <li>This subroutine is called from the main program by the <i>JSUB</i> (<i>Jump to Subroutine</i>) instruction.</li> <li>At the end of the subroutine, an <i>RSUB (Return from Subroutine)</i> instruction returns to the instruction <i>following the JSUB</i>.</li> </ul> |                                                                                                                                                                                                                                                                                                        |                              |

### **Sample Subroutine Call (Cont.)**

| SIC/XE                                                                                         | JSUB | READ      | CALL READ SUBROUTINE $L \leftarrow (PC); PC \leftarrow READ$        |

|------------------------------------------------------------------------------------------------|------|-----------|---------------------------------------------------------------------|

|                                                                                                | •    |           |                                                                     |

| ↓                                                                                              |      |           | SUBROUTINE TO READ 100-BYTE RECORD                                  |

| READ                                                                                           | LDX  | #0        | INITIALIZE INDEX REGISTER TO 0 $X \leftarrow 0$                     |

|                                                                                                | LDT  | #100      | INITIALIZE REGISTER T TO 100 T $\leftarrow$ 100                     |

| RLOOP                                                                                          | TD   | INDEV     | TEST INPUT DEVICE Test device specified by (INDEV)                  |

|                                                                                                | JEQ  | RLOOP     | LOOP IF DEVICE IS BUSY PC   RLOOP if CC set to =                    |

|                                                                                                | RD   | INDEV     | READ ONE BYTE INTO REGISTER A A                                     |

|                                                                                                | STCH | RECORD, X | STORE DATA BYTE INTO RECORD RECORD + (X) $\leftarrow$ (A)           |

|                                                                                                | TIXR | т         | ADD 1 TO INDEX AND COMPARE TO 100 $X \leftarrow (X) + 1; (X) : (T)$ |

|                                                                                                | JLT  | RLOOP     | LOOP IF INDEX IS LESS THAN 100 PC   RLOOP if CC set to <            |

|                                                                                                | RSUB |           | EXIT FROM SUBROUTINE $PC \leftarrow (L)$                            |

|                                                                                                | •    |           |                                                                     |

|                                                                                                |      |           |                                                                     |

|                                                                                                | •    |           |                                                                     |

| INDEV                                                                                          | BYTE | X'F1'     | INPUT DEVICE NUMBER                                                 |

| RECORD                                                                                         | RESB | 100       | 100-BYTE BUFFER FOR INPUT RECORD                                    |

| <ul> <li>Register T: Store 100 for the number of bytes to read.</li> </ul>                     |      |           |                                                                     |

| <ul> <li>Register X: Indicate the offset (index value) to the starting of an array.</li> </ul> |      |           |                                                                     |

# **CISC Machines**

## **CISC Machines**

- Complex instruction set computers (CISC) usually include

- A relatively large and complicated instruction set.

- Several different instruction formats and lengths.

- Many different addressing modes.

- The implementation of CISC architecture in hardware tends to be complex.

- Sample CISC machines

- -VAX architecture

- Pentium architecture

### **VAX Architecture**

#### Memory

- Bytes and words

- 8 bits form a **byte**.

- 2 bytes form a *word*.

- 4 bytes form a *longword*.

- 8 bytes form a *quadward*.

- 16 bytes form a *octaword*.

- Some operations are more efficient when operands are aligned in a particular way.

- E.g., a *longword* operand that begins at a byte address that is a multiple of 4.

- Virtual address space: 2<sup>32</sup> bytes

- This virtual memory allows program to operate as though they have a large memory.

- One half of virtual address space is **system space** that contains the operating system and is shared by all programs.

- The other half of the address space is *process space* that is defined *separately for each program*.

- A part of the process space contains stacks that are available to the program.

### VAX Architecture (Cont.)

### Registers

- 16 general-purpose registers denoted by *R0* through *R15.*

- R15 is the program counter (PC).

- · It is updated during instruction execution to point to the *next instruction*.

- R14 is the stack pointer (SP).

- · It points to the *current top of the stack* in the program's *process space*.

- R13 is the frame pointer (FP).

- VAX procedure call conventions build a data structure called a stack frame, and place its address in FP.

- R12 is the argument pointer (AP).

- The procedure call convention uses AP to pass a *list of arguments* associated with the call.

- R6 through R11 have no special functions.

- *R0 through R5* are likewise available for general use, but are also used by some machine instructions.

- A processor status longword (PSL) that contains state variables and flags associated with a process.

## **VAX Architecture (Cont.)**

#### Data Formats

hexadecimal F for positive numbers and hexadecimal D for negative numbers

- Integers are stored as binary numbers in a byte, word, longword, quadword, or octaword.

- 2's complement representation is used for negative values.

- Characters are stored using their 8-bit ASCII codes.

- Four different floating-point data formats, ranging in length from 4 to 16 bytes.

- VAX processors provide a *packed decimal* data format.

- Each byte represents two decimal digits, with each digit encoded using 4 bits of the byte. (4 bits form a *nibble*.)

- The sign is encoded in the last 4 bits.

- VAX also provides hardware to support *queues* and *variable-length bit strings*.

- There are single machine instructions that

- · Insert and remove entries in queues. (support atomic operations)

- Perform a variety of operations on bit strings. Copyright © All Rights Reserved by Yuan-Hao Chang

## **VAX Architecture (Cont.)**

#### Instruction formats

- VAX machine instructions use a variable-length instruction format.

- Each instruction consists of

- An operation code (1 or 2 bytes)

- Up to six operand specifiers, depending on the type of instruction.

- Each operand specifier designates one of the VAX addressing modes and gives any additional information to locate the operand.

#### Addressing modes

- Register mode: The operand itself is in a register.

- Register deferred mode: The address of an operand is specified by a register.

- The register contents may be automatically incremented or decremented by the operand length (*autoincrement* and *autodecrement* modes).

- There are several base relative addressing modes, with displacement fields of different lengths.

- E.g., PC-relative mode by using register PC for the displacement.

- *Immediate addressing* is to include operands in the instruction itself.

- All of the addressing modes could include an *index register*, and many of them are available in a form that specifies *indirect addressing*.

Copyright © All Rights Reserved by Yuan-Hao Chang

### VAX Architecture (Cont.)

#### Instruction set

- Instruction *mnemonics* are formed by combining the following elements:

- 1. a prefix that specifies the type of operations,

- 2. a suffix that specifies the data type of the operands,

- 3. a *modifier* (on some instructions) that gives *the number of operands involved*.

- E.g.,

- **ADDW2**: an add operation with *two* operands, and each a word in length.

- MULL3: a multiply operation with three longword operands.

- CVTWL: a conversion from word to longword, with two operands.

- Operands may be located in registers, memory, or instruction itself (immediate addressing).

- VAX provides all of the usual types of instructions for *computation*, *data movement and conversion*, *comparison*, *branching*, etc.

### **VAX Architecture (Cont.)**

### Instruction set (Cont.)

- There are a number of operations that are much more complex than the machine instructions found on most computers.

- These operations are hardware realizations of frequently occurring sequences of codes. E.g.,

- Instructions to load and store *multiple registers*, and manipulate *queues* and *variable-length bit fields*.

- · Powerful instruction to call and return from procedures.

- Single instruction to

- » Save a designated set of registers,

- » Pass a list of arguments to the procedure,

- » Maintain the stack, frame, and argument pointers, and

- » Set a mask to enable error traps for arithmetic operations.

# VAX Architecture (Cont.)

### Input and output

- Input and output are accomplished by I/O device controllers.

- Each controller has a set of control/status and data registers, which are assigned locations in the *physical* address space.

- The address space mapped by the device controller registers are called **I/O** space.

- No special instructions are required to access registers in I/O space.

- An I/O device driver issues commands to the device controller by storing values into the appropriate *registers*, exactly as if there were physical memory locations.

- The association of an address in I/O space with a physical register in a device controller is handled by the *memory* management routines.

Copyright © All Rights Reserved by Yuan-Hao Chang

### **Pentium Architecture**

### Memory

- At the physical level, memory consists of 8-bit bytes. All addresses used are byte addresses.

- Programmers view the x86 memory as a collection of segments.

- An address consists of two parts: A segment number and an offset.

- Segments can be of different sizes, and are often used for different purposes. E.g., a segment for executable instructions or data storage.

- A segment can be divided into *pages*. Some of the pages of a segment may be in physical memory, while others may be stored on disk.

- The segment/offset address specified by the programmer is automatically translated into a physical byte address by the x86 *Memory Management Unit (MMU)*.

#### Registers

- Eight general-purpose registers (32 bits):

- *EAX, EBX, ECX, and EDX* are generally used for data manipulation. It is possible to access individual words or bytes from these registers.

- ESI, EDI, EBP, and ESP are usually used to hold addresses.

- EIP is a 32-bit register that contains a pointer to the next instruction to be executed. (like program counter (PC))

- FLAGS is a 32-bit register that contains many different bit flags.

- Some indicates the status of the processor.

- Others are used to record the results of comparisons and arithmetic operations.

- Six 16-bit segment registers to locate segments in memory.

- Segment register **CS** contains the address of the *currently executing code segment*.