計畫成員 : 張原豪、陳郁方

隨著數據的爆炸性增長,傳統von Neumann構構在處理需要大量數據移動的機器學習演算法和深度神經網路等各種應用時,面臨效率低下的問題。為了解決此一問題,本合作計畫旨在研究「以記憶體為中心」的計算架構和加速器,以提升下一代機器學習、神經網絡和量子模擬/驗證應用的執行效率。此計畫的主題為選擇適當的記憶體中心設計(Memory-Centric Design)架構,以利用記憶體與儲存體特性來達成運算加速的目的。記憶體中心設計的概念就是把一些運算從處理單元(如CPU、GPU和FPGA)移到記憶體中或儲存裝置中來進行處理,以大幅降低資料移動所造成的效能瓶頸問題。本計畫的重點將包括記憶體內運算(processing-in-memory, PIM)、近記憶體運算(processing-near-memory, PNM)和存儲體內運算(in-storage computing, ISC)等三個記憶體中心設計的研究方向。

計畫初期成果

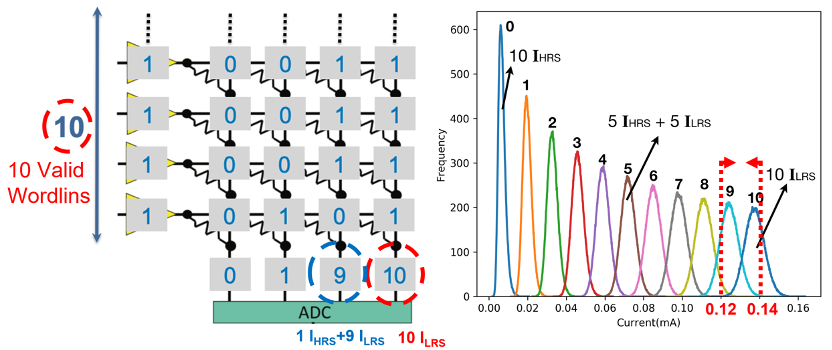

在記憶體中心設計方面,我們的團隊率先解決ReRAM Crossbar的可擴展性問題,並率先讓NAND快閃記憶體具備支援記憶體內運算(PIM)的能力。我們通過解決ReRAM Crossbar類比變異誤差(analog variation error)的問題,以解決其擴展性問題,因為ReRAM Crossbar是通過設置不同的輸入電壓和電阻值,利用類比訊號來進行乘加操作(MAC),並通過輸出電流來確定結果。基於這樣的觀察,我們提出一種自適應數據操作策略,通過權重轉移設計和自適應輸入子週期設計來解決類比變異誤差問題。這一結果被發表在頂尖國際會議ACM/IEEE EMSOFT'20和頂尖國際期刊IEEE TCAD’20。

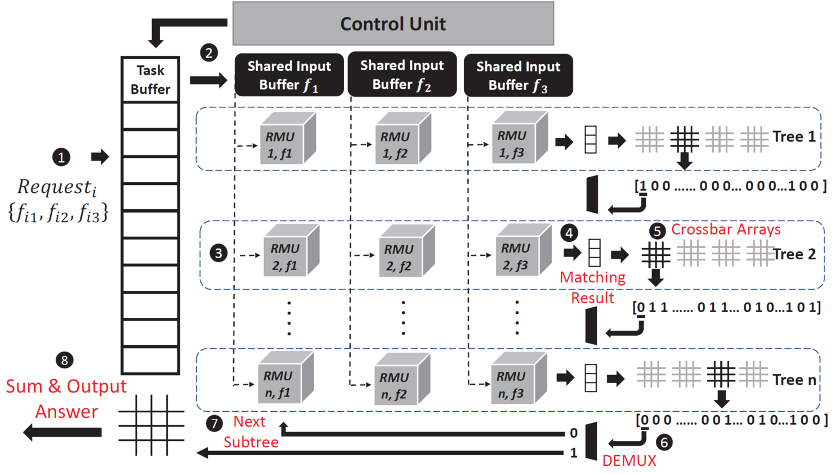

解決擴展性問題後,我們將研究重點擴展到如何使用ReRAM Crossbar陣列來提升稀疏圖(sparse graph)的處理效能。我們提出了一個圖形感知的方案,其中包括系統性的預處理方法,以更好地利用ReRAM Crossbar加速器上的操作單元。同時,這個方案還包含一個本地索引壓縮方法,可以進一步精煉圖形數據壓縮的能力,以解決局部稀疏性問題。在一系列的實驗中證明,我們所提出的方案可以提升ReRAM Crossbar陣列的利用率達31.4%,並且能夠節省能源達17.2%。同時,此一研究已被頂尖國際會議ACM/IEEE ISLPED'21和頂尖國際期刊ACM/IEEE ICCAD'22接受。此外,我們亦利用ReRAM Crossbar來提升隨機森林(random forest)的推論效能達3.13倍之多,並且已被頂尖國際會議ACM/IEEE DAC'23接受。

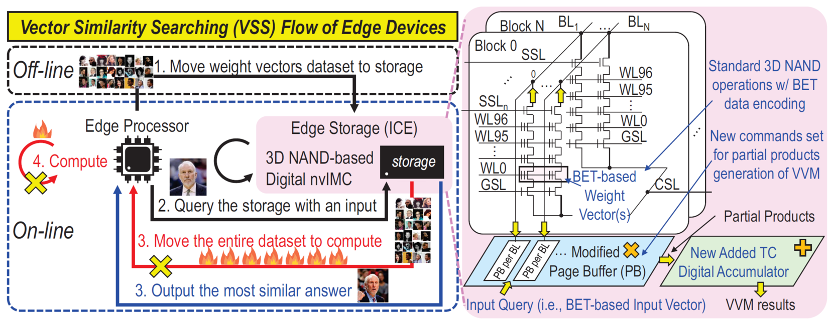

此外,我們同時關注機器學習中關於非結構化向量的向量相似性搜索(vector similarity search , VSS)議題,其中VSS是經常被使用在如人臉搜索這樣的應用之中。為了避免VSS需要從NAND快閃記憶體和DRAM記憶體之間進行過多的資料移動,我們開發了智能認知引擎(intelligent cognition engine , ICE),這是一種基於3D NAND快閃記憶體發展而來記憶體內運算架構,用於加速VSS的處理。在所提出的ICE設計中,我們開發了一種免除ADC/DAC轉換硬體的記憶體內運算技術,此技術具有極高的記憶體設計密度。同時,我們還提出了一種bit-error-tolerance data encoding技術,以減輕資料計算時的可靠性問題,並促進向量-向量乘法(VVM)運算的平行度,從而技升VSS的計算速度。實驗結果顯示,我們的ICE設計可以將系統性能提高17倍至95倍,能源效率提高11倍至140倍之多。這項研究已被計算機架構領域三個最佳會議之一的ACM / IEEE MICRO 2022接受發表。在過去的幾十年中,台灣只有很少數的研究人員在此會議上發表過論文。此外,我們還開發了一種基於3D-NAND快閃記憶體的記憶體內運算技術,用以支持邊緣人工智能設備上的相似向量匹配(SVM)運算操作,此研究已發表在頂尖國際會議IEEE ISSCC’22之上。

未來展望

未來,我們將繼續研究利用記憶體中心設計(Memory-Centric Design)架構來對下一代量子模擬/驗證、機器學習演算法和神經網路運算加速的關鍵技術。同時,我們將解決(1)記憶體中心運算架構的選擇問題、(2)新興非揮發性記憶體技術(例如 ReRAM、PCM、MRAM 和快閃記憶體)對記憶體內運算的支援問題、(3)基於目標應用和硬體設計特性的優化策略問題以及(4)用於性能驗證的模擬平台發展問題。同時,我們也會持續針對計畫主要研究目標進行研究,包括(1)研究如何利用記憶體內運算(PIM)架構發展新的應用、(2)研究如何利用近記憶體運算(PNM)架構發展大型計算應用,以及(3)研究如何優化儲存體內運算(ISC)的設計。